基于FPGA的智能函数发生器的设计学生姓名:XX学生学号:20XXXXXXXXX一、设计要求1

设计一个能产生递增、递减斜波,方波,三角波,正弦波,阶梯波智能函数发生器;2

要求能自主选择输出波形,并能调整输出频率

二、设计原理递增、递减斜波是以一定常数递增、递减来产生的

三角波的产生是在输出波形的前半周期内从0累加到最大值255(8位),在后半周期从最大值递减到0来实现的

阶梯波阶梯波是以一定的常数递增的

正弦波的产生原理是基于奈奎斯特采样定律,先对模拟信号采集,经过量化后存入查表中,再由相位累加器产生地址,通过对查表寻址,得到离散化波形序列,最后经过D/A转换输出模拟波形

方波的产生是在输出波形的前半周期输出低电平,后半周期输出高电平,从而得到占空比为50%的方波信号

通过所设计的智能函数发生器可以得到递增、递减斜波,方波,三角波,正弦波和阶梯波六种波形,这些波形的产生都是通过FPGA的核心芯片,各种运算都在FPGA中进行,直接输出选择的波形

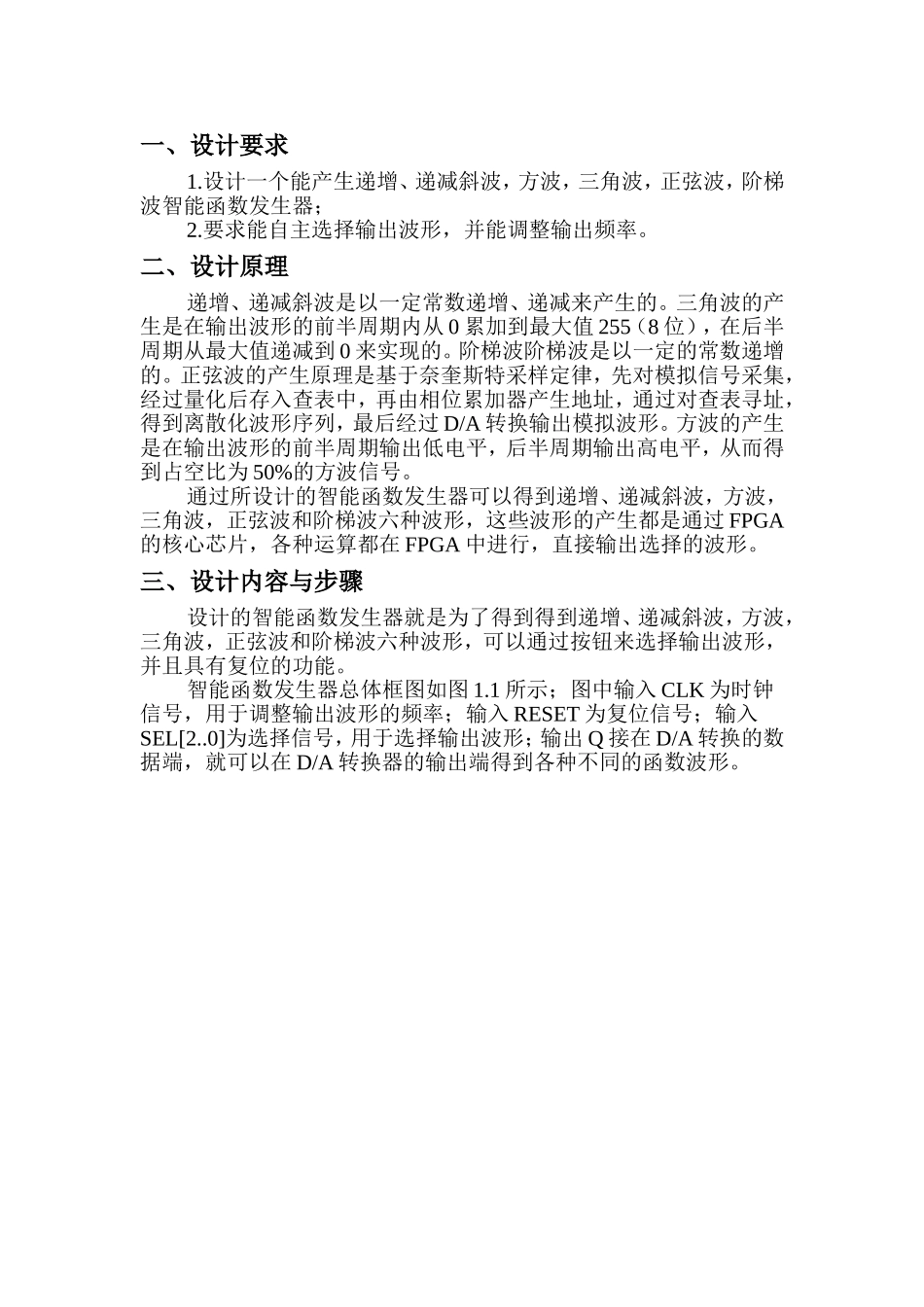

三、设计内容与步骤设计的智能函数发生器就是为了得到得到递增、递减斜波,方波,三角波,正弦波和阶梯波六种波形,可以通过按钮来选择输出波形,并且具有复位的功能

智能函数发生器总体框图如图1

1所示;图中输入CLK为时钟信号,用于调整输出波形的频率;输入RESET为复位信号;输入SEL[2

0]为选择信号,用于选择输出波形;输出Q接在D/A转换的数据端,就可以在D/A转换器的输出端得到各种不同的函数波形

1智能函数发生器总体框图1

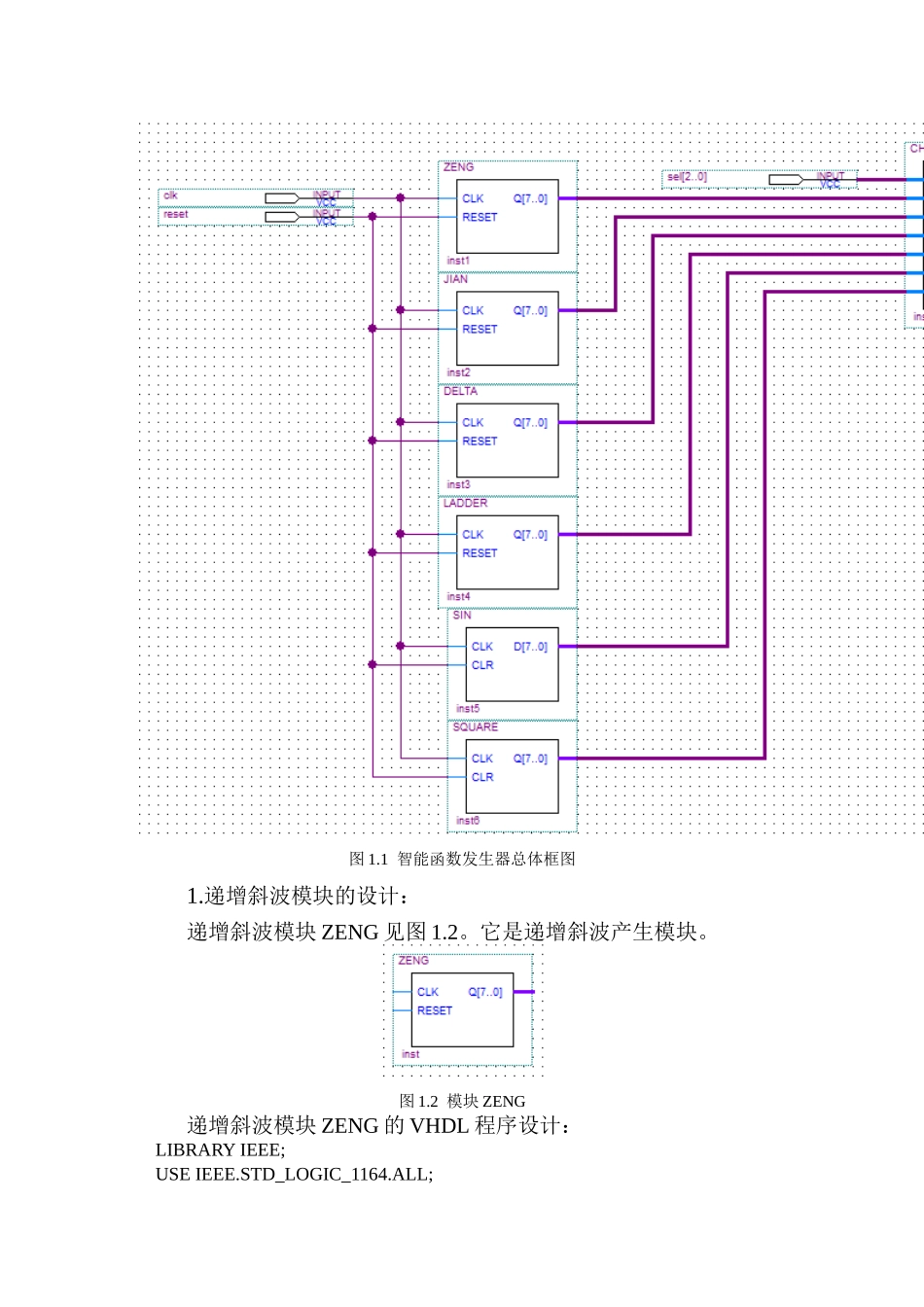

递增斜波模块的设计:递增斜波模块ZENG见图1

它是递增斜波产生模块

2模块ZENG递增斜波模块ZENG的VHDL程序设计:LIBRARYIEEE;USEIEEE

STD_LOGIC_1164

ALL;USEIEEE

STD_LOGIC_UNSIGNED

ALL;ENTITYZENGISPO