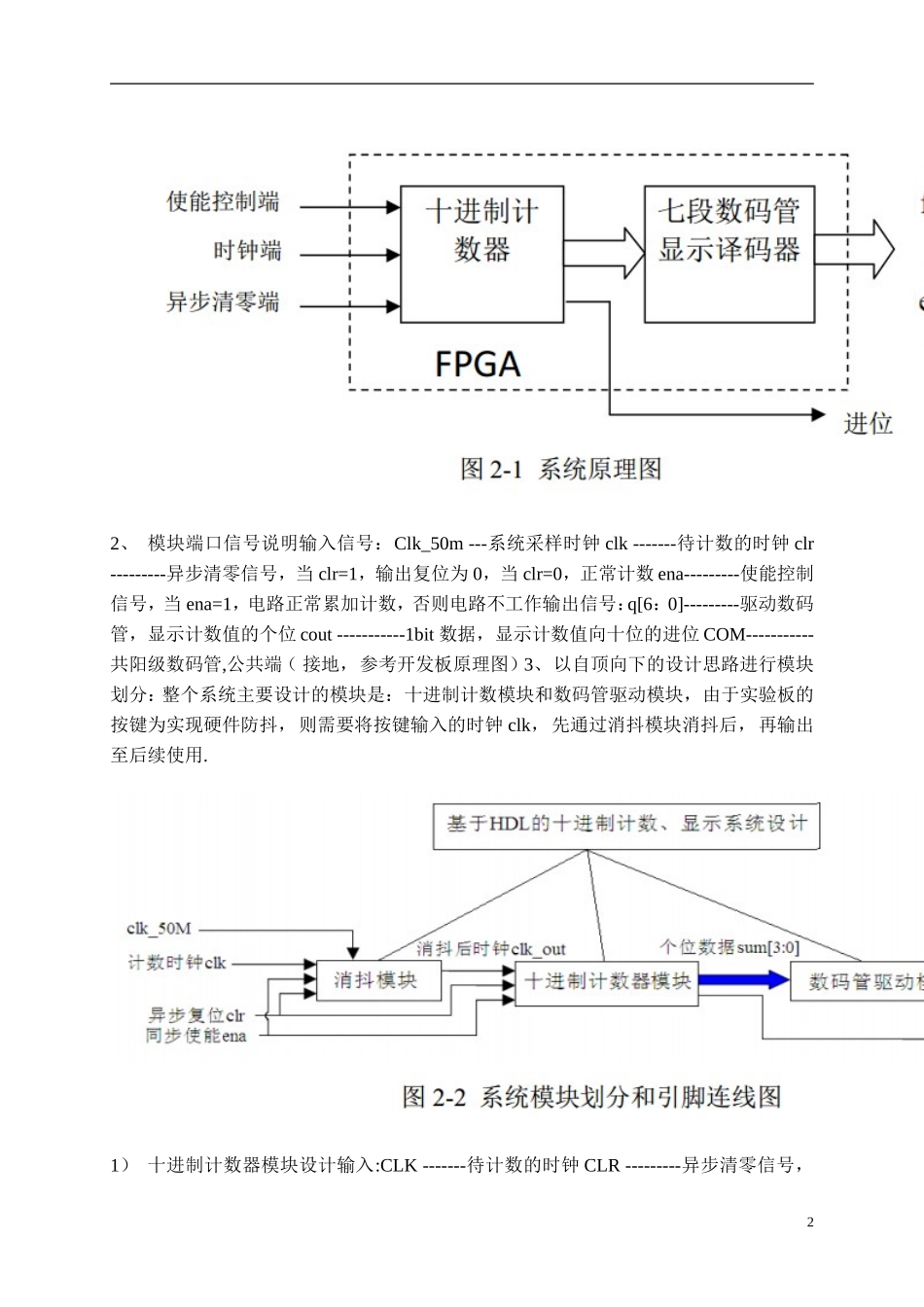

****大学实验报告课程名称:FPGA技术实验名称:基于原理图的十进制计数器设计姓名:*****学号:*****班级:电子1202指导教师:***********大学****学院制实验二基于HDL十进制计数、显示系统设计一、实验原理1、实验内容:设计具有异步复位、同步使能的十进制计数器,其计数结果可以通过七段数码管、发光二极管等进行显示

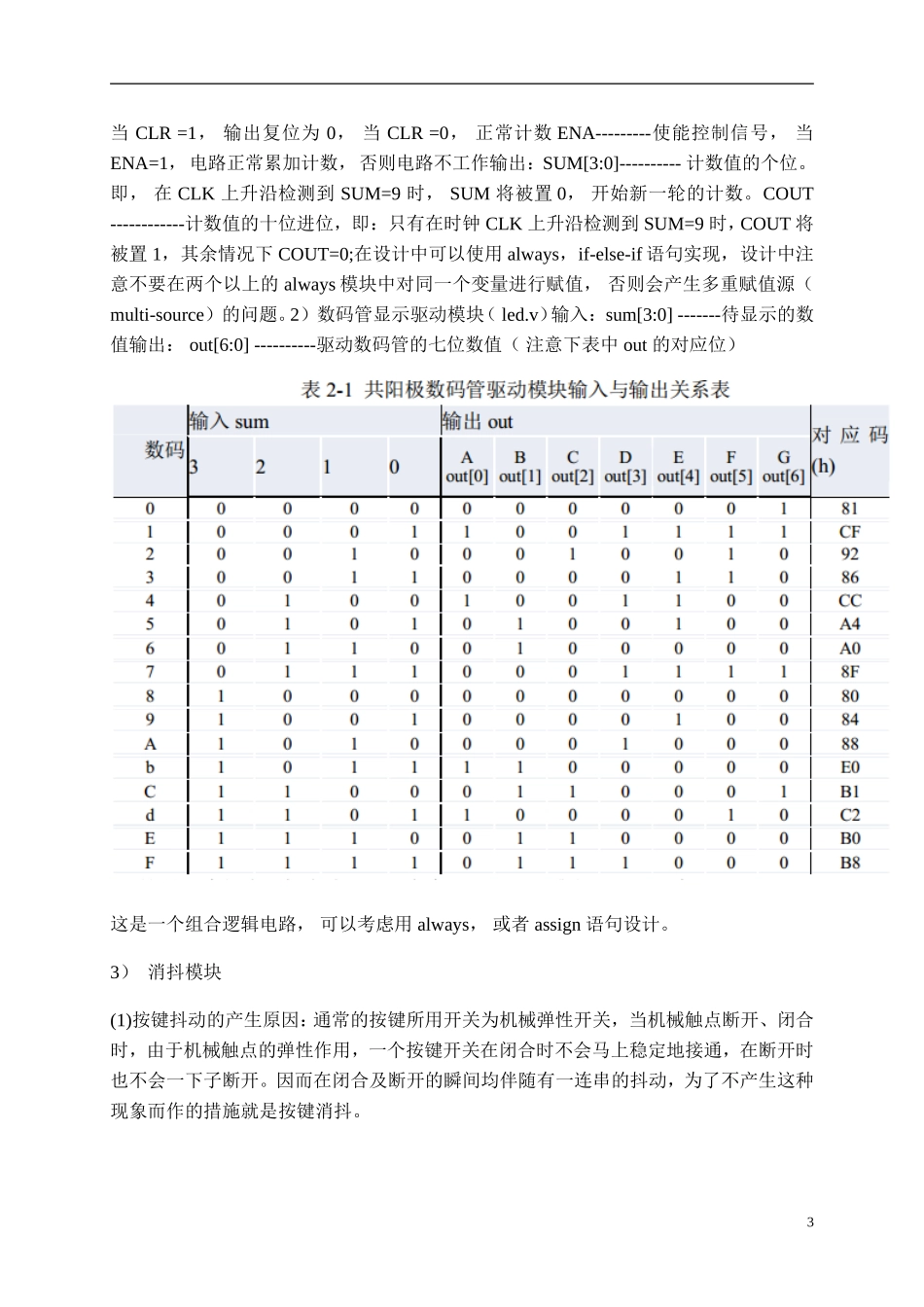

2、模块端口信号说明输入信号:Clk_50m---系统采样时钟clk-------待计数的时钟clr---------异步清零信号,当clr=1,输出复位为0,当clr=0,正常计数ena---------使能控制信号,当ena=1,电路正常累加计数,否则电路不工作输出信号:q[6:0]---------驱动数码管,显示计数值的个位cout-----------1bit数据,显示计数值向十位的进位COM-----------共阳级数码管,公共端(接地,参考开发板原理图)3、以自顶向下的设计思路进行模块划分:整个系统主要设计的模块是:十进制计数模块和数码管驱动模块,由于实验板的按键为实现硬件防抖,则需要将按键输入的时钟clk,先通过消抖模块消抖后,再输出至后续使用

1)十进制计数器模块设计输入:CLK-------待计数的时钟CLR---------异步清零信号,2当CLR=1,输出复位为0,当CLR=0,正常计数ENA---------使能控制信号,当ENA=1,电路正常累加计数,否则电路不工作输出:SUM[3:0]----------计数值的个位

即,在CLK上升沿检测到SUM=9时,SUM将被置0,开始新一轮的计数

COUT------------计数值的十位进位,即:只有在时钟CLK上升沿检测到SUM=9时,COUT将被置1,其余情况下COUT=0;在设计中可以使用always,if-else-if语句实现,设计中注意不要在两个以上的