第二章第二章TMS320C2000TMS320C2000系列系列DSPDSP的内核结构的内核结构2

1TMS320C20002

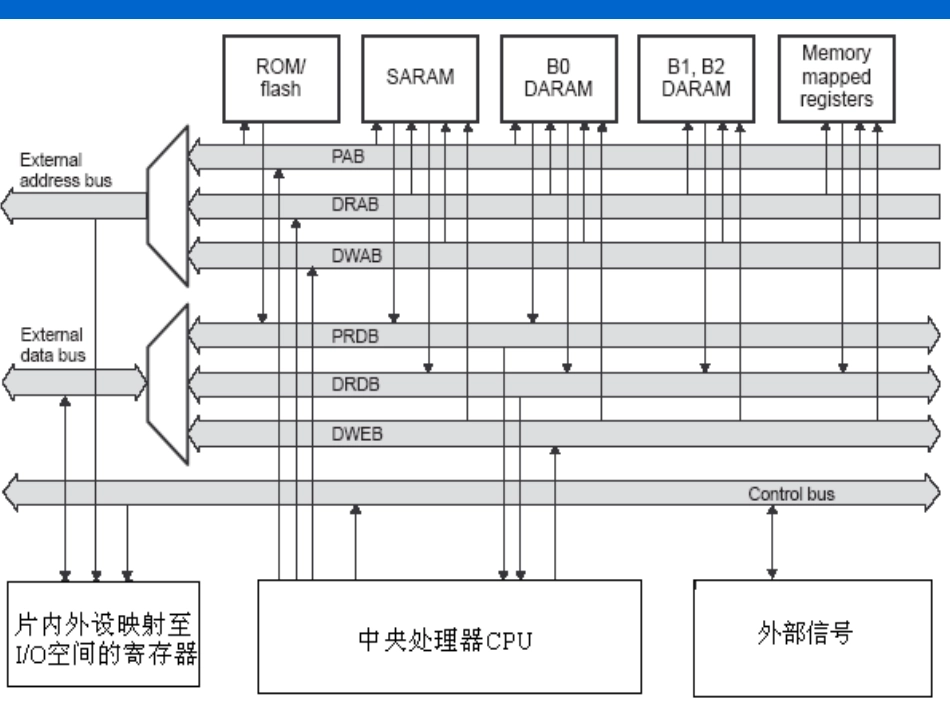

1TMS320C2000的总线结构的总线结构总线分类:数据总线:提供数据存储器和程序存储器内容;地址总线:提供存储器的地址信息;控制总线:控制存储器的读、写操作;表表2

1总线名称及功能总线名称及功能总线简总线简称称总线类别总线类别功能功能PABPAB程序地址总线程序地址总线提供程序存储器读提供程序存储器读//写地址写地址PRDBPRDB程序读数据总程序读数据总线线将指令、立即操作数从程序空间送至将指令、立即操作数从程序空间送至cpucpuDRABDRAB数据读地址总数据读地址总线线提供读数据存储器地址提供读数据存储器地址DWADWABB数据写地址总数据写地址总线线提供写数据存储器地址提供写数据存储器地址DRDBDRDB数据读数据总数据读数据总线线将数据存储器中内容送至将数据存储器中内容送至CPUCPUDWEBDWEB数据写数据总数据写数据总线线将数据送至程序存储器和数据存储器将数据送至程序存储器和数据存储器与微处理器与微处理器80888088和单片机和单片机80518051总线相比总线相比,,DSPDSP的总线具有以下特点:的总线具有以下特点:((11)具有分离的程序和数据总线,允许同时访问程序)具有分离的程序和数据总线,允许同时访问程序和数据存储器空间;和数据存储器空间;((22)具有独立的数据)具有独立的数据R/WR/W地址总线和数据读写总线,地址总线和数据读写总线,是是CPUCPU对数据存储器的读、写操作可在一个机器周期对数据存储器的读、写操作可在一个机器周期内完成;内完成;((33)分离的程序和数据空间及独立总线结构,支持)分离的程序和数据空间及独立总线结构,支持CPUCPU在单机器时钟内并行执行算术、逻辑和位处理操在单机器时