张晨曦刘依1/181

主存的主要性能指标:延迟和带宽2

以往:Cache主要关心延迟,I/O主要关心带宽3

现在:Cache关心两者4

下面讨论几种能提高主存性能的存储器组织技术5

在下面的讨论中,我们以处理Cache失效为例来说明各种存储器组织结构的好处

6主存第五章存储层次张晨曦刘依2/18◆增加Cache块大小能利用主存带宽增加所带来的好处在以下的讨论中,我们假设基本存储器结构的性能为:5

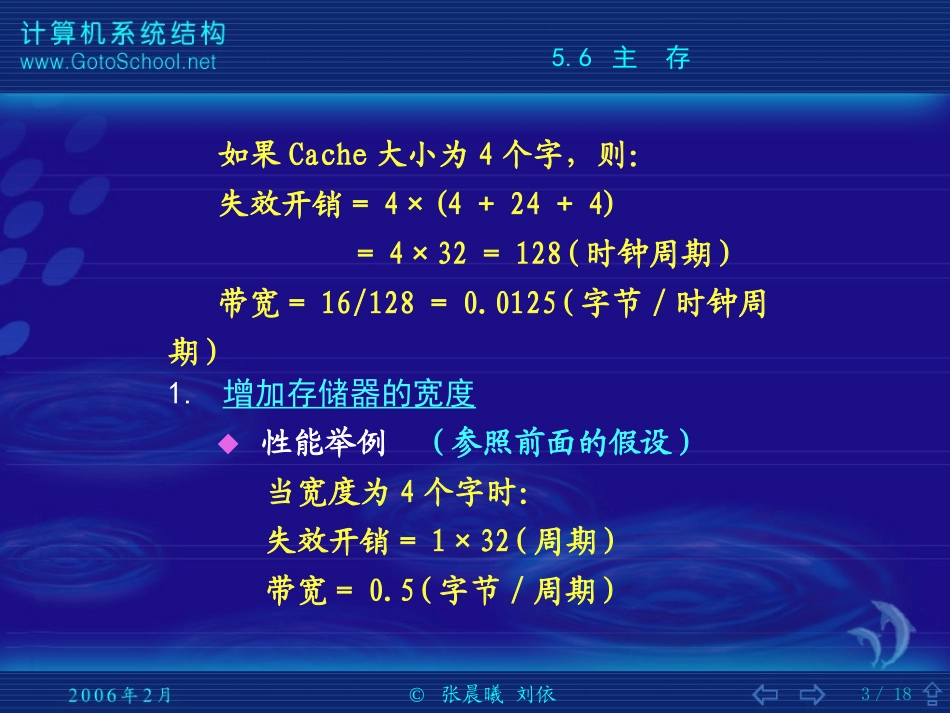

6主存送地址需4个时钟周期每个字的访问时间为24个时钟周期传送一个字的数据需4个时钟周期◆为了减少失效开销TM,应该:减少主存延迟提高主存带宽张晨曦刘依3/18如果Cache大小为4个字,则:失效开销=4×(4+24+4)=4×32=128(时钟周期)带宽=16/128=0

0125(字节/时钟周期)1

增加存储器的宽度◆性能举例(参照前面的假设)当宽度为4个字时:失效开销=1×32(周期)带宽=0

5(字节/周期)5

6主存张晨曦刘依5/18◆缺点:5

6主存增加CPU和存储器之间的连接通路的宽度CUP和Cache之间有一个多路选择器扩充主存的最小增量增加了相应的倍数写入有可能变得复杂◆举例:DEC的AlphaAxp21064:256位宽2

采用简单的多体交叉存储器在存储系统中采用多个DRAM,并利用它们潜在的并行性

张晨曦刘依7/18◆存储器的各个体一般是按字交叉的交叉存储器(interleavedmemory)通常是指存储器的各个体是按字交叉的

字交叉存储器非常适合于处理:Cache读失效,写回法Cache中的写回性能举例:(参照前面的假设)失效开销=4+24+4×4=44(周期)带宽=0

4(字节/周期)5

6主存张晨曦刘依8/18假设四个存储体的地址是在字一级交叉的,即存储体0中每个字的地址对4取模都是0,体1中每个字的地址对4取模都是1