QCA电路的设计方法用数字信号完成对数字量进行算术运算和逻辑运算的电路称为数字电路或数字系统

由于它具有逻辑运算和逻辑处理功能,所以又称数字逻辑电路

现代的数字电路由半导体工艺制成的若干数字集成器件构造而成

逻辑门是数字逻辑电路的基本单元

存储器是用来存储二值数据的数字电路

从整体上看,数字电路可以分为组合逻辑电路和时序逻辑电路两大类

组合逻辑电路为了用QCA设计组合逻辑电路,我们需要一种能够表示布尔函数的方法

在QCA中,最佳的设计是使用多数逻辑门

这与传统数字电路中使用与门和或门之间,仅仅是因技术的改变引起逻辑风格的变化,但是关于设计风格的固有观念仍然相同

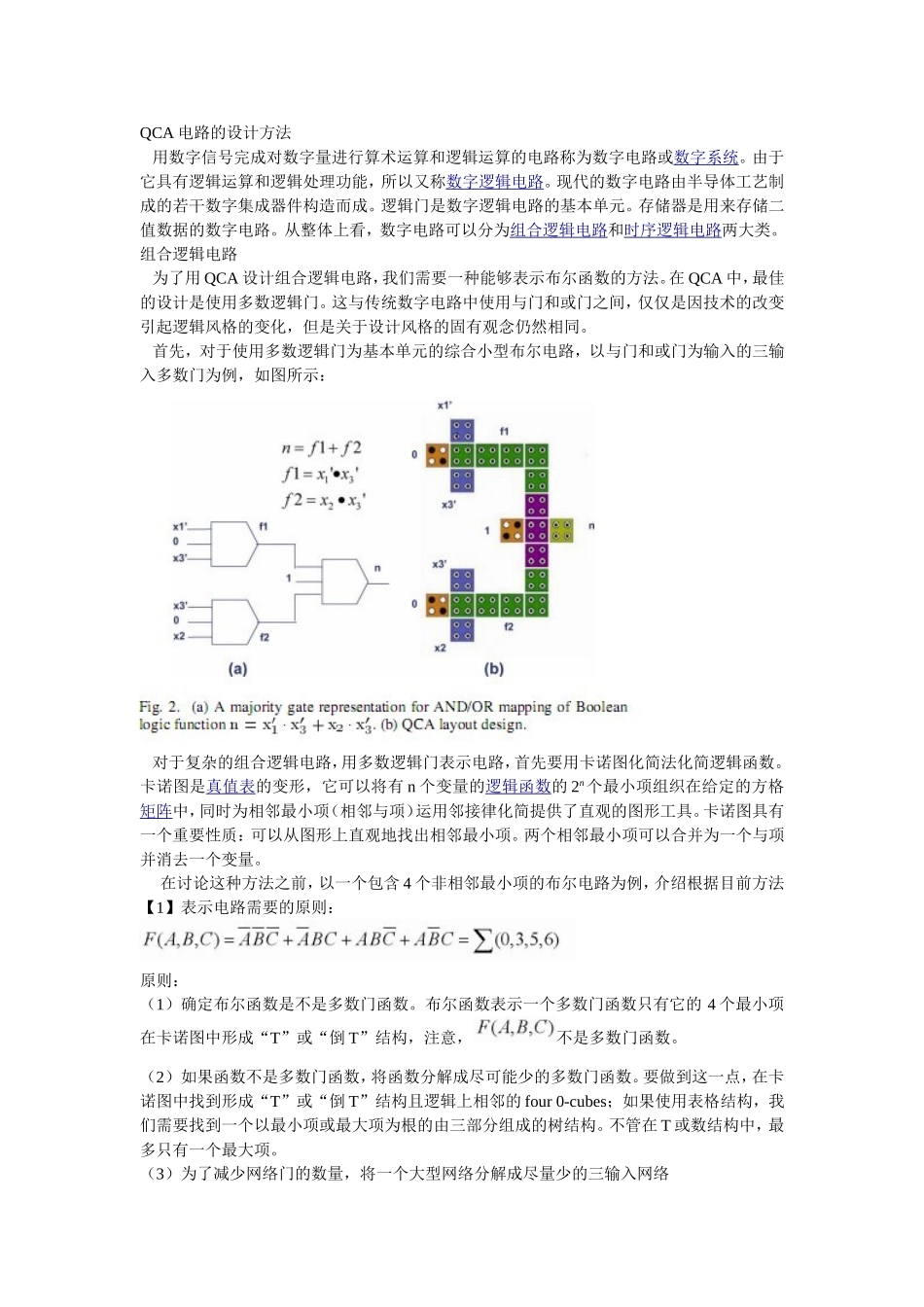

首先,对于使用多数逻辑门为基本单元的综合小型布尔电路,以与门和或门为输入的三输入多数门为例,如图所示:对于复杂的组合逻辑电路,用多数逻辑门表示电路,首先要用卡诺图化简法化简逻辑函数

卡诺图是真值表的变形,它可以将有n个变量的逻辑函数的2n个最小项组织在给定的方格矩阵中,同时为相邻最小项(相邻与项)运用邻接律化简提供了直观的图形工具

卡诺图具有一个重要性质:可以从图形上直观地找出相邻最小项

两个相邻最小项可以合并为一个与项并消去一个变量

在讨论这种方法之前,以一个包含4个非相邻最小项的布尔电路为例,介绍根据目前方法【1】表示电路需要的原则:原则:(1)确定布尔函数是不是多数门函数

布尔函数表示一个多数门函数只有它的4个最小项在卡诺图中形成“T”或“倒T”结构,注意,不是多数门函数

(2)如果函数不是多数门函数,将函数分解成尽可能少的多数门函数

要做到这一点,在卡诺图中找到形成“T”或“倒T”结构且逻辑上相邻的four0-cubes;如果使用表格结构,我们需要找到一个以最小项或最大项为根的由三部分组成的树结构

不管在T或数结构中,最多只有一个最大项

(3)为了减少网络门的数量,将一个大型网络分解成尽量少的三输入网络基于上