对高速信号线匹配问题的分析一、问题的提出在研发过程中,有设计人员提出,在850(CPU)的地址线上不应该加匹配串联电阻,并主张在原来设计中有串联匹配电阻的要去掉

但根据高速信号设计原则,对高速高频信号线必须根据实际布局情况考虑信号线的匹配,否则有可能引起信号完整性问题,产生大的过冲或振玲等现象,使设计留下隐患

为了明确上述问题,我们做了以下工作

二、试验分析为了对加匹配串联电阻和不加匹配串联电阻这二种情况进行比较,我们进行了下面的测试

测试的原理简图见图1,PCB布局见图2

测试是在收信板BRX上进行的

将BRX通电跑起来后,对850的一根地址线进行了测试,测试数据为其244的一根输出线上所带三个负载输入端的信号波形

850(CPU)的时钟由50MHz晶振分频提供,其工作频率为25MHz

测试的原理简图见图1,图1测试的原理简图测试了以下几种情况:1

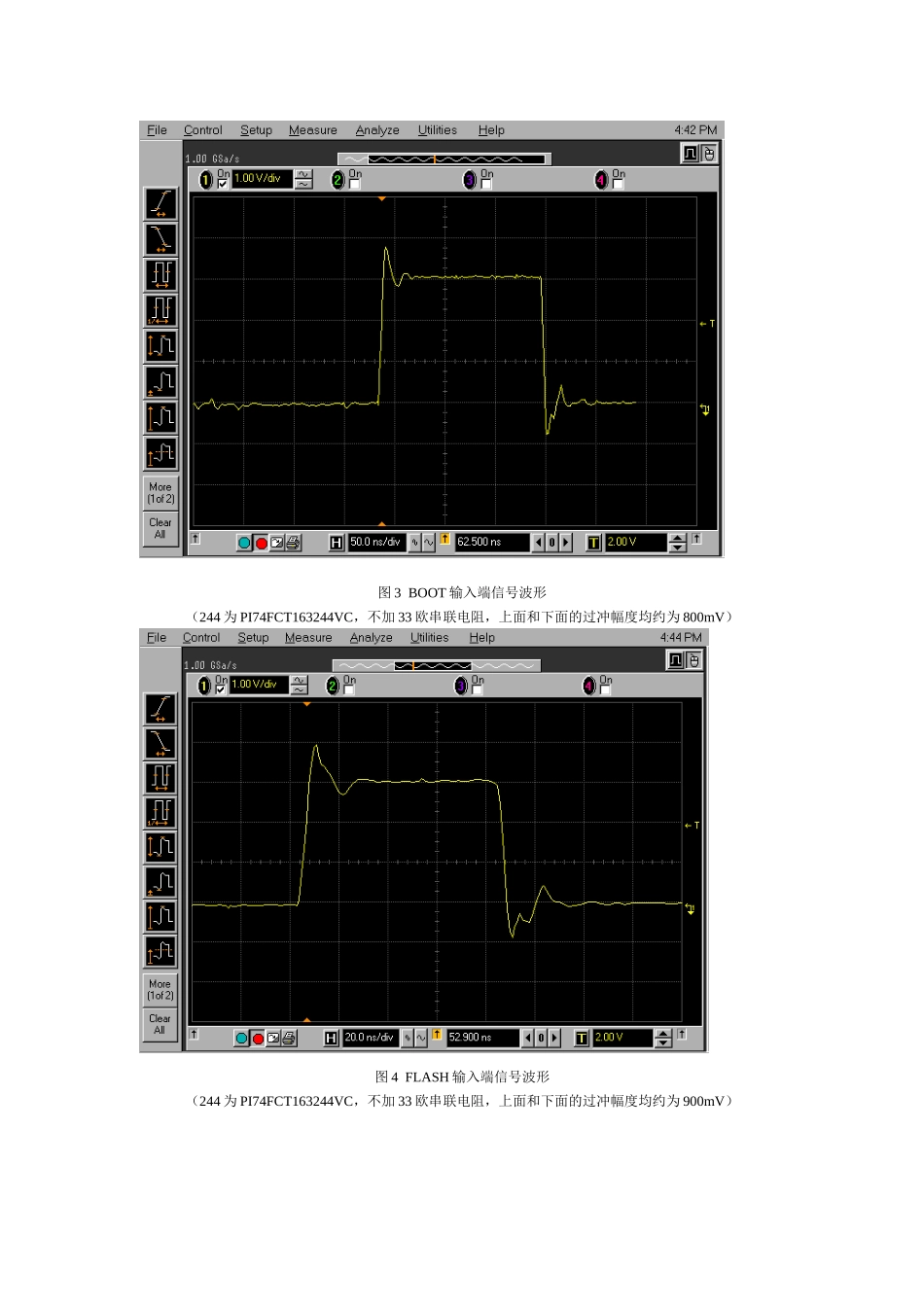

244的型号为PI74FCT163244VC,驱动输出端不加33欧串联电阻,测试结果见图3、图4、图5

244的型号为PI74FCT163244VC,驱动输出端加33欧串联电阻,测试结果见图6、图7、图8

244的型号为PI74ALVCH162244V,驱动输出端不加33欧串联电阻,测试结果见图9、图10、图11

244的型号为PI74ALVCH162244V,驱动输出端加33欧串联电阻,测试结果见图12、图13、图14

上面测试了二种型号的244,分别为PI74FCT163244VC和PI74ALVCH162244V,二种型号的封装一致,主要区别在于,在PI74ALVCH162244V的输出端,内部等效串联了一个25欧的电阻,而PI74FCT163244VC没有

测试结果:33Ω850(CPU)244BootFlashFPGAR20cm10cm:测试点R:外置匹配电阻其中图3BOOT输入端信号波形(244为PI7