封装体叠层(PoP,Package-on-Package)技术在逻辑电路和存储器集成领域,封装体叠层(PoP)已经成为业界的首选,主要用于制造高端便携式设备和智能手机使用的先进移动通讯平台

移动便携市场在经历2009年的衰退之后,已经显示反弹迹象,进入平稳增长阶段,相比而言,智能手机的增长比其它手机市场更快,占据的市场份额正不断增加

与此同时,PoP技术也在移动互联网设备、便携式媒体播放器等领域找到了应用

这些应用带来了对PoP技术的巨大需求,而PoP也支持了便携式设备对复杂性和功能性的需求,成为该领域的发动机

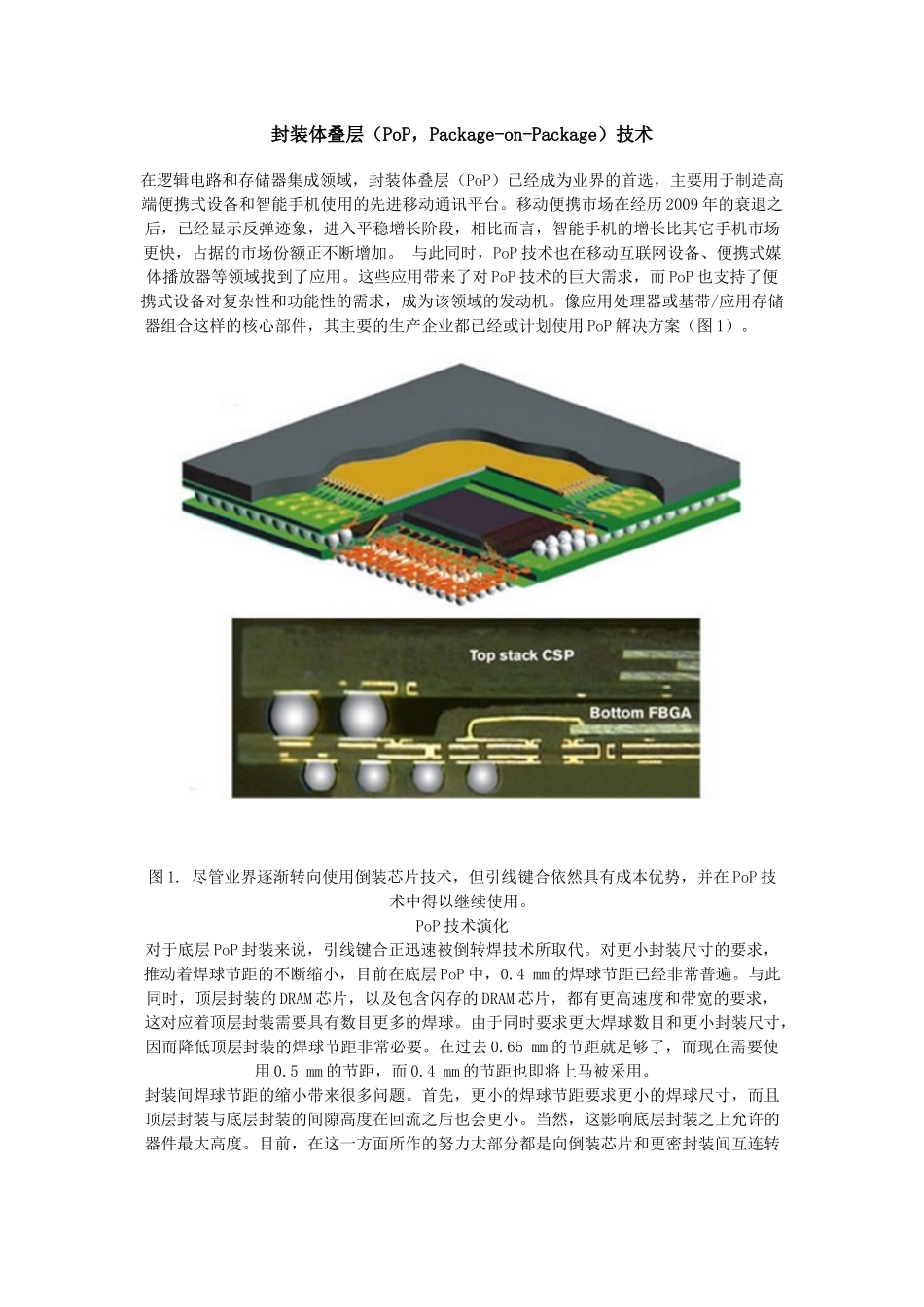

像应用处理器或基带/应用存储器组合这样的核心部件,其主要的生产企业都已经或计划使用PoP解决方案(图1)

\:b,g7]%U"}0t$a*`图1

尽管业界逐渐转向使用倒装芯片技术,但引线键合依然具有成本优势,并在PoP技术中得以继续使用

PoP技术演化对于底层PoP封装来说,引线键合正迅速被倒转焊技术所取代

对更小封装尺寸的要求,推动着焊球节距的不断缩小,目前在底层PoP中,0

4mm的焊球节距已经非常普遍

与此同时,顶层封装的DRAM芯片,以及包含闪存的DRAM芯片,都有更高速度和带宽的要求,这对应着顶层封装需要具有数目更多的焊球

由于同时要求更大焊球数目和更小封装尺寸,因而降低顶层封装的焊球节距非常必要

65mm的节距就足够了,而现在需要使用0

5mm的节距,而0

4mm的节距也即将上马被采用

5x4])~7V;i封装间焊球节距的缩小带来很多问题

首先,更小的焊球节距要求更小的焊球尺寸,而且顶层封装与底层封装的间隙高度在回流之后也会更小

当然,这影响底层封装之上允许的器件最大高度

目前,在这一方面所作的努力大部分都是向倒装芯片和更密封装间互连转变,以满足对更小封装尺寸和叠层高度的要求(图2)

随着PoP技术的演变,封装体的尺寸、高度和焊球节