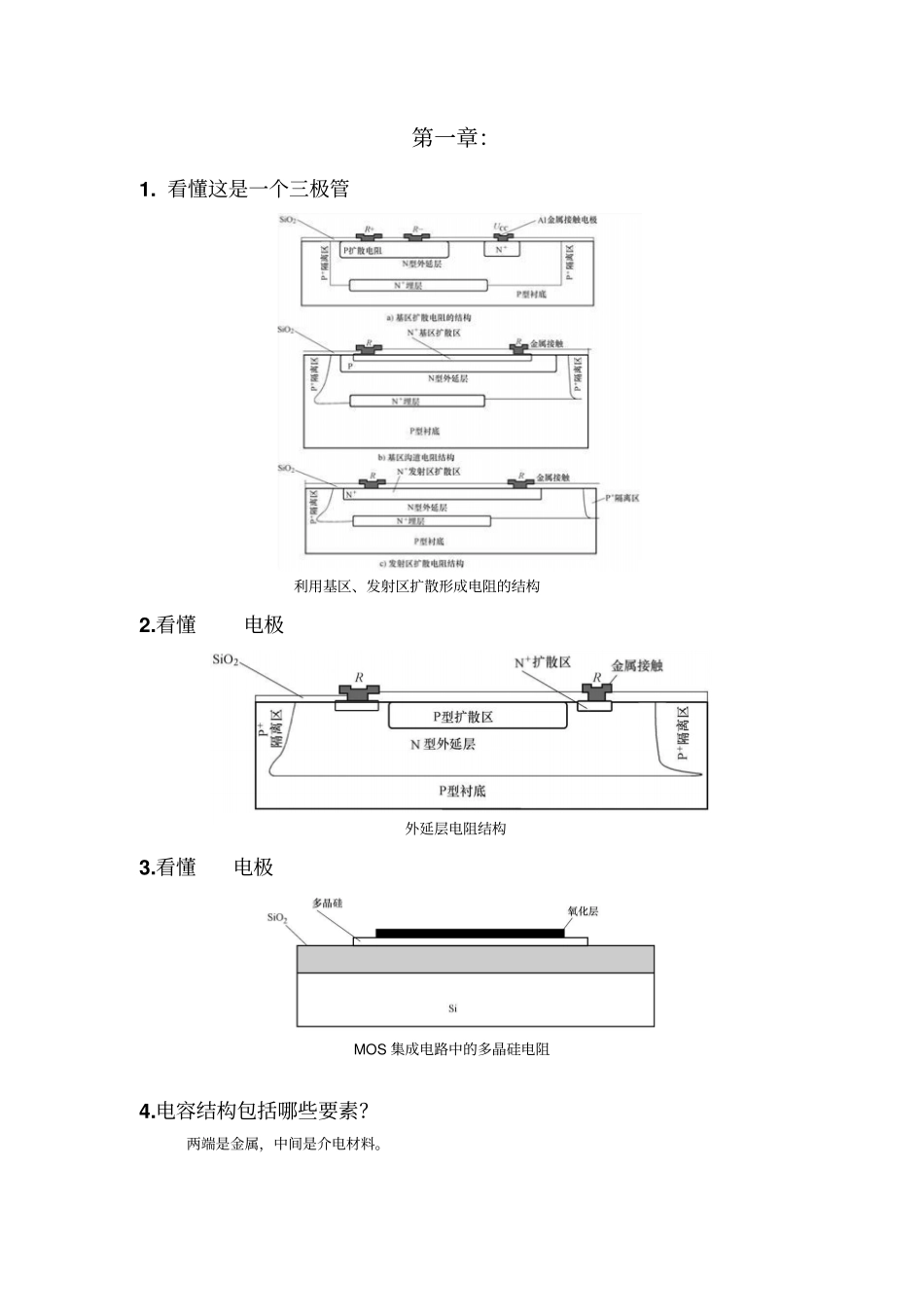

看懂这是一个三极管利用基区、发射区扩散形成电阻的结构2

看懂电极外延层电阻结构3

看懂电极MOS集成电路中的多晶硅电阻4

电容结构包括哪些要素

两端是金属,中间是介电材料

集成电路中电容的结构5

这是电容结构Pn结位于空间电荷区,是一个电容结构

PN结电容结构6

MOS场效应晶体管中以SiO2为栅极层MOS场效应晶体管电容结构7

二极管,三极管,MOS管集成电路中二极管的基本结构8

看懂二极管,三极管的结构集成电路中二极管的结构9

三极管分清npn与pnp

结构上,NPN三极管的中间是P区(空穴导电区),两端是N区(自由电子导电区),而PNP三极管正相反

使用上,NPN三极管工作时是集电极接高电压,发射极接低电压,基极输入电压升高时趋向导通,基极输入电压降低时趋向截止;而PNP三极管工作时则是集电极接低电压,发射极接高电压,基极输入电压升高时趋向截止,基极输入电压降低时趋向导通

晶体管的基本结构10

什么叫NMOS

什么叫PMOS

PMOS是指利用空穴来传导电性信号的金氧半导体

NMOS是指利用电子来访传导电性信号的金氧半晶体管

MOS管的结构图和示意图11

集成电路包括哪些阶段

阶段:硅片(晶圆)的制备、掩膜版的制作、硅片的制造及元器件封装集成电路制造的阶段划分半导体芯片的制造框图半导体芯片制造的关键工艺12

硅的基本性质

硅的禁带宽度较大(1

12eV),硅半导体的工作温度可以高达200℃

硅片表面可以氧化出稳定且对掺杂杂质有极好阻挡作用的氧化层(SiO2)优点:(1)硅的丰裕度硅是地球上第二丰富的元素,占到地壳成分的25%,经合理加工,硅能够提纯到半导体制造所需的足够高的纯度,而消耗的成本比较低

(2)更高的熔化温度允许更宽的工艺容限硅的熔点是1412℃,远高于锗937℃的熔点,更高的熔点使得硅可以承受高