卷积交织器与解交织器的Verilog实现卷积交织器与解交织器的Verilog实现-1-交织器与解交织器的Verilog设计0引言在数字通信中由于信道固有的噪声特性以及衰落特性,信息在有干扰信道传输时不可避免的会发生差错

为了提高通信系统信息传输的可靠性,一般采用纠错编码技术来提高通信系统抗干扰能力

但是当信道发生突发差错时,会造成连续的错误,超过纠错码的纠错能力

交织技术作为一项改善通信系统性能的方式,将数据按照一定的规则打乱,把原先连续的差错分散开来,使突发性错误转化为随机性错误,能够提高通信系统抗突发差错的能力和降低译码复杂度

VHDL作为一种硬件设计时采用的标准语言,降低设计FPGA的难度,使整个系统的设计和调试周期缩短

本设计利用FPGA实现交织,能大大缩减电路的体积,提高电路的稳定性

1卷积交织和解交织的原理交织过程可算作一个编码过程,他把经过纠错编码的数据进行一定的排列组合,提高原有纠错编码的纠突发错误的能力

数字通信中一般采取的同步交织有2种:(1)块交织也叫矩阵行列转置法

可以表述为一个二维存储器阵列(N×B)

交织过程是数据先按行写入,再按列读出;解交织过程则相反,是数据先按列写入,再按行读出

块交织结构简单,但数据延时时间长而且所需的存储器比较大

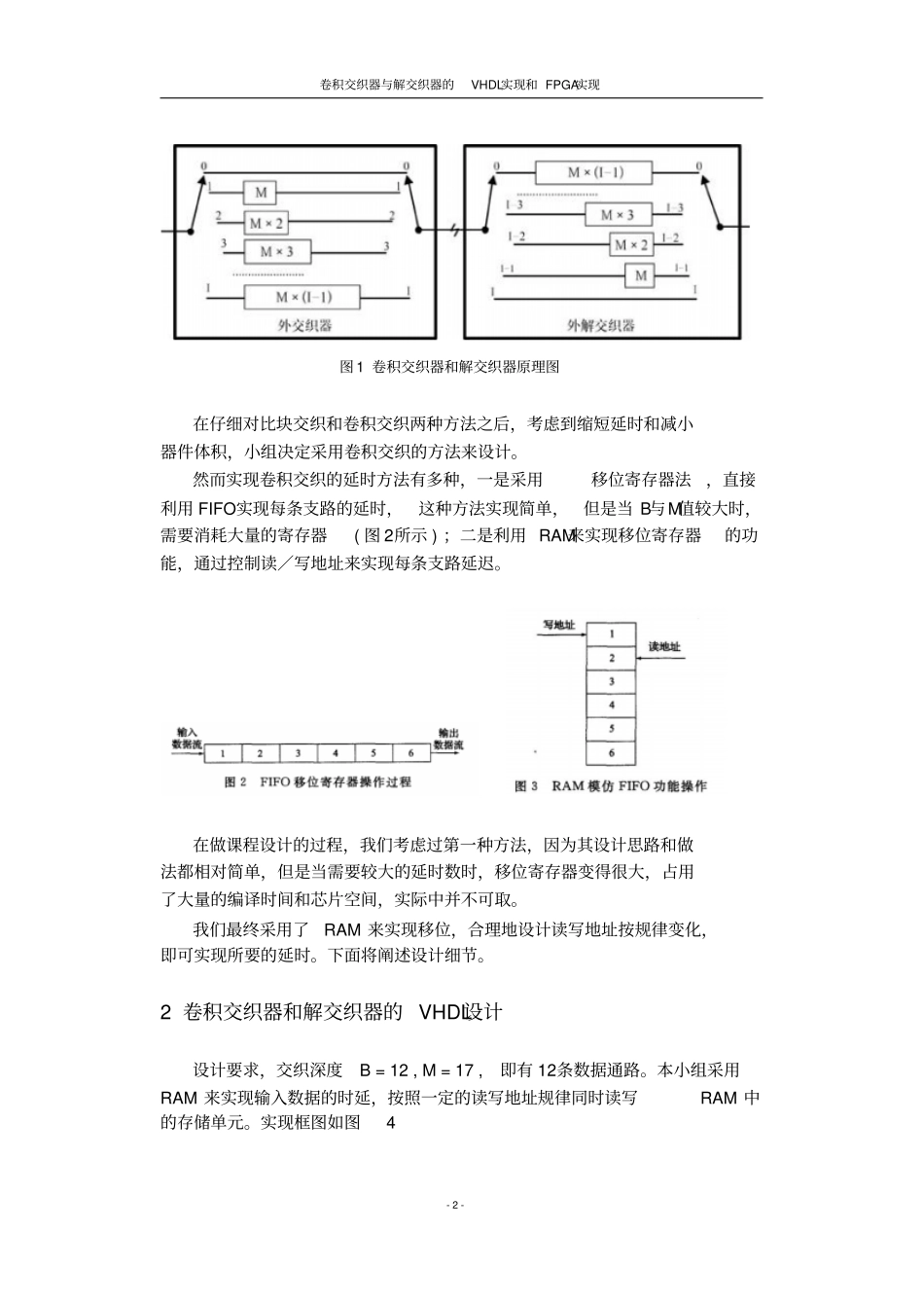

(2)卷积交织交织器的输入端的输入符号数据按顺序分别进入B条支路延时器,每一路延时不同的符号周期

第一路无延时,第二路延时M个符号周期,第三路延时2M个符号周期,⋯,第B路延时(B-1)M个符号周期

交织器的输出端按输入端的工作节拍分别同步输出对应支路经延时的数据

卷积交织每条支路符号数据的延时节拍为di=(i-1)MB,i=1,2,⋯,B

解交织器的延时数与交织器相反

卷积交织器与解交织器的VHDL实现和FPGA实现-2-图1卷积交织器和解交织器原理图在仔细对比块交织和卷积交织两种方法之后,考虑到缩短延时和减