使用D触发器设计一个11001序列检测器讨论使用D触发器设计一个11001序列检测器,讨论序列可交迭(Overlap)检测和不可交迭检测在设计上的区别,讨论分别采用Mealy机设计和采用Moore机设计的区别,讨论未用状态的处理问题

【要求】给出电路原理图或HDL代码,要求进行仿真,并给出仿真结果

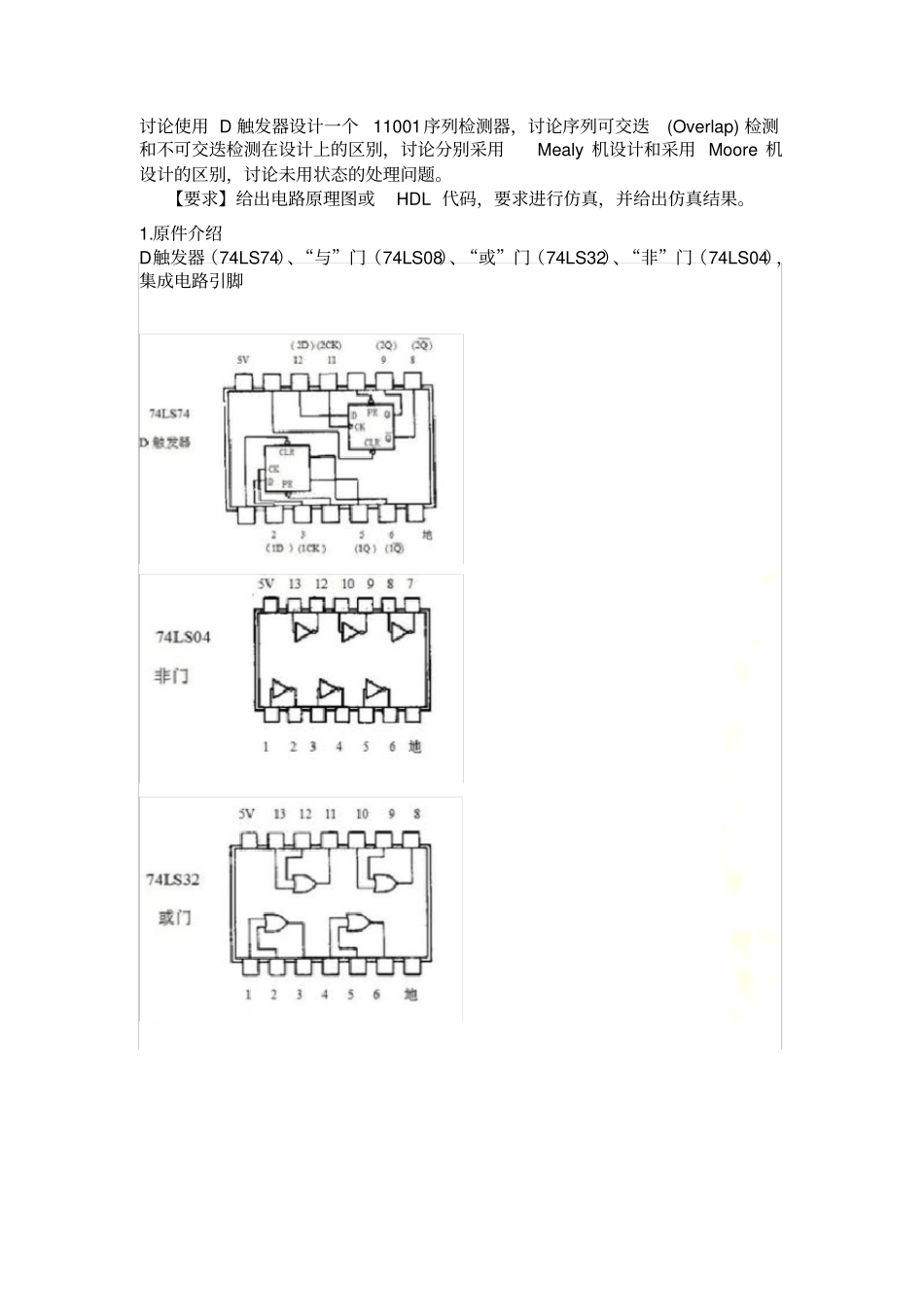

原件介绍D触发器(74LS74)、“与”门(74LS08)、“或”门(74LS32)、“非”门(74LS04),集成电路引脚2

设计思路根据要求,设计的序列检测器有一个外部输入x和一个外部输出Z

输入和输出的逻辑关系为:当外部输入x第一个为"1",外部输出Z为"0";当外部输入x第二个为"1",外部输出Z为"0";当外部输入第三个x为"0",外部输出Z为"0",当外部输入第四个x为“0”,外部输出Z为0,当外部输入第五个x为“1”,外部输出Z为“1”

假定有一个外部输入x序列以及外部输出Z为:输入X011100101输出Y000000100要判别序列检测器是否连续接收了"11001",电路必须用不同的状态记载外部输入x的值

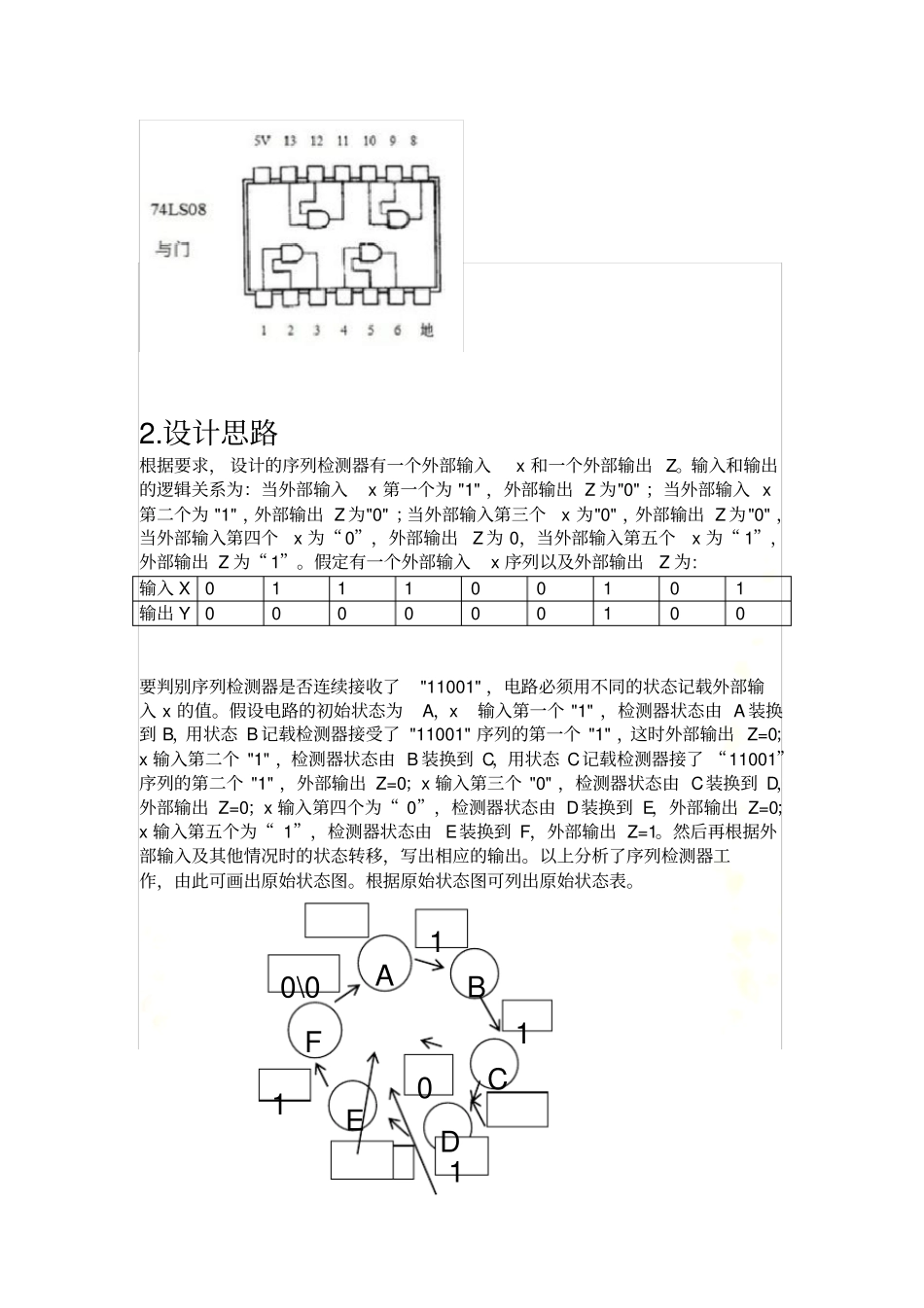

假设电路的初始状态为A,x输入第一个"1",检测器状态由A装换到B,用状态B记载检测器接受了"11001"序列的第一个"1",这时外部输出Z=0;x输入第二个"1",检测器状态由B装换到C,用状态C记载检测器接了“11001”序列的第二个"1",外部输出Z=0;x输入第三个"0",检测器状态由C装换到D,外部输出Z=0;x输入第四个为“0”,检测器状态由D装换到E,外部输出Z=0;x输入第五个为“1”,检测器状态由E装换到F,外部输出Z=1

然后再根据外部输入及其他情况时的状态转移,写出相应的输出

以上分析了序列检测器工作,由此可画出原始状态图

根据原始状态图可列出原始状态表

ABDCEF1110\001状态转换表现态X01AA\0B\0BA\0C\0CD