74LS160 芯片同步十进制计数器(直接清零) ·用于快速计数的内部超前进位 ·用于 n 位级联的进位输出 ·同步可编程序 ·有置数控制线 ·二极管箝位输入 ·直接清零 ·同步计数 本电路是由 4 个主从触发器和用作除 2 计数器及计数周期长度为除 5 的 3 位 2 进制计数器所用的附加选通所组成

有选通的零复位和置 9 输入

为了利用本计数器的最大计数长度(十进制),可将 B 输入同 QA 输出连接,输入计数脉冲可加到输入 A 上,此时输出就如相应的功能表上所要求的那样

LS90 可以获得对称的十分频计数,办法是将 QD 输出接到 A 输入端,并把输入计数脉冲加到 B 输入端,在 QA 输出端处产生对称的十分频方波

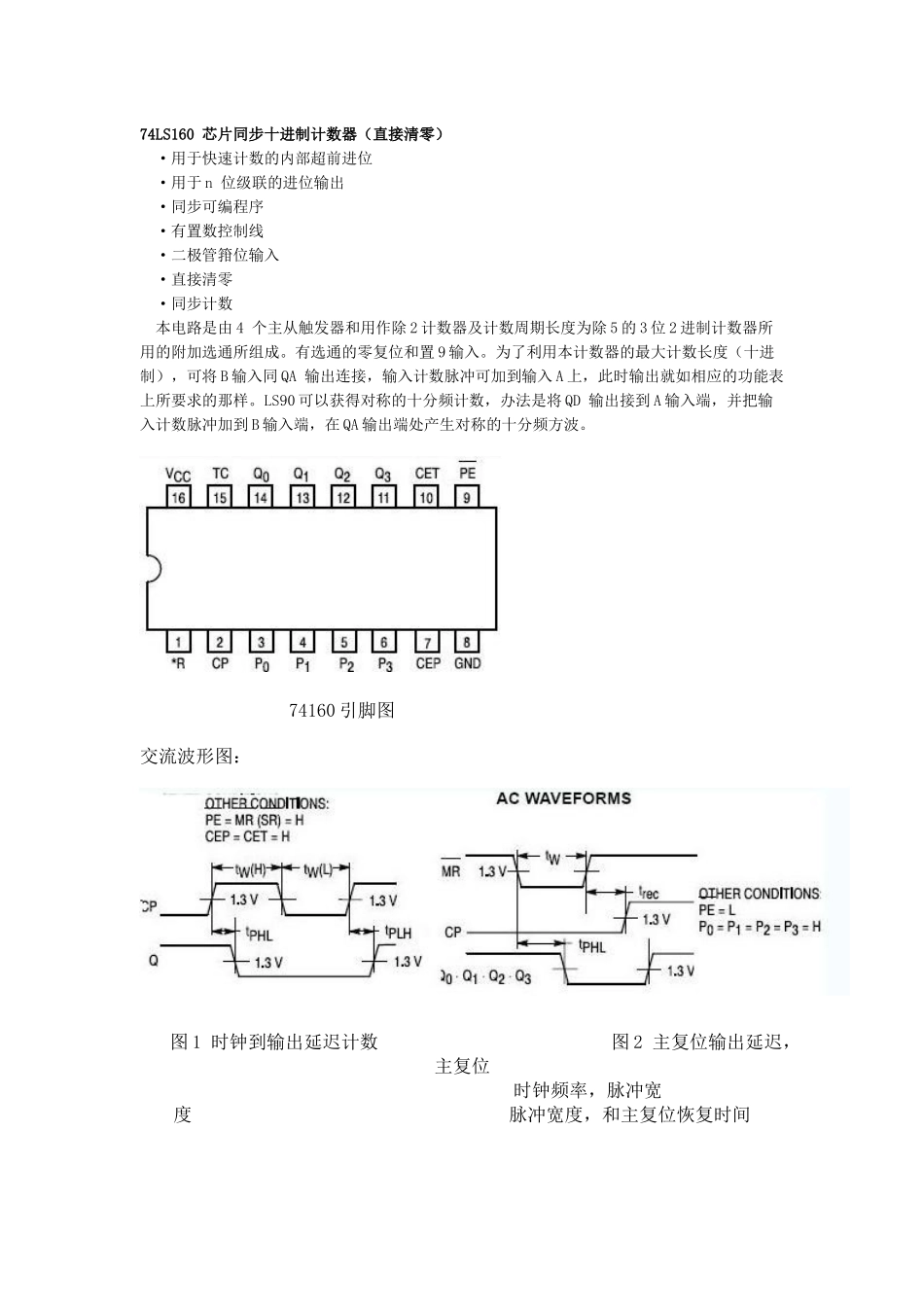

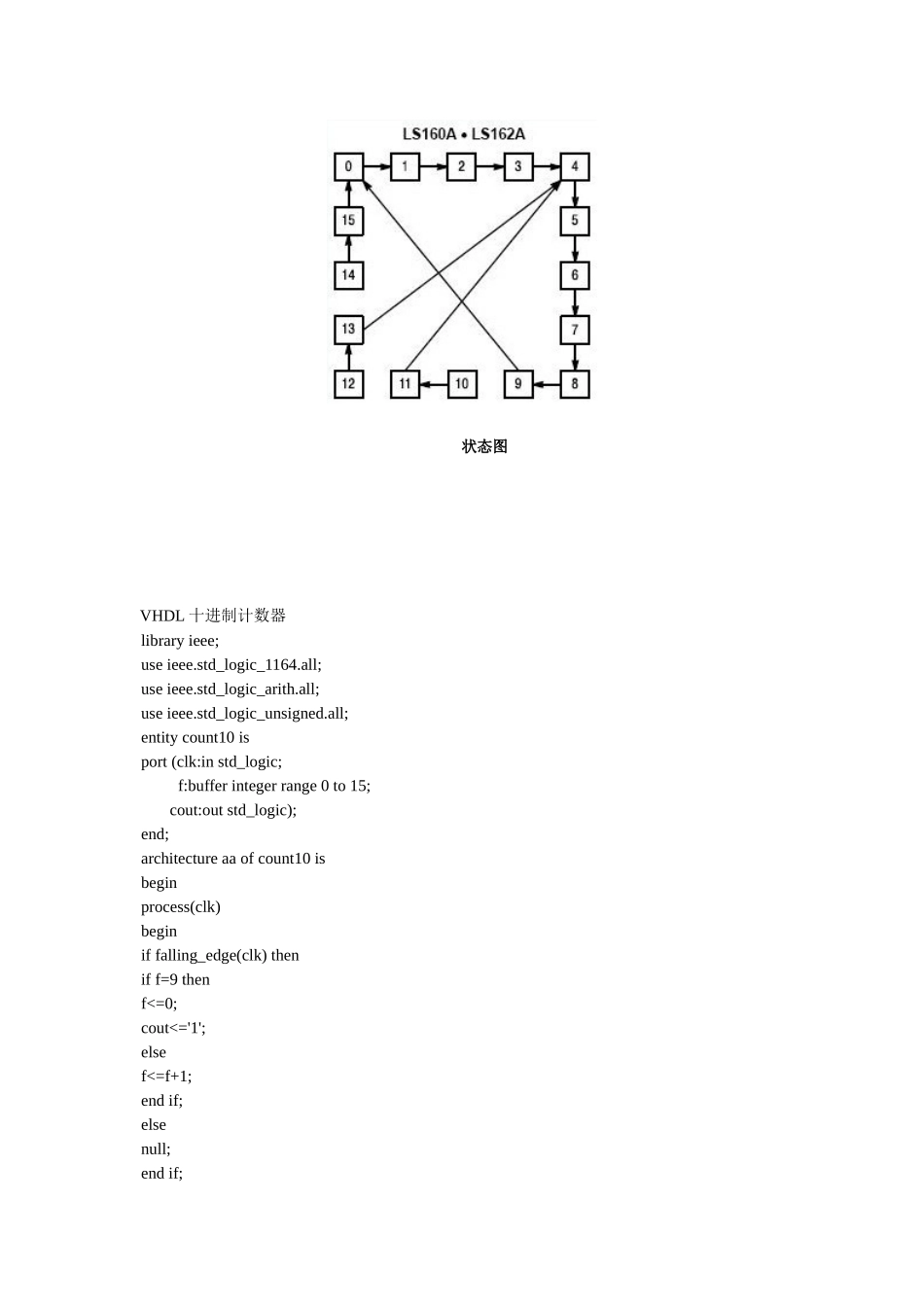

74160 引脚图交流波形图: 图 1 时钟到输出延迟计数 图 2 主复位输出延迟,主复位 时钟频率,脉冲宽度 脉冲宽度,和主复位恢复时间状态图VHDL 十进制计数器library ieee;use ieee

std_logic_1164

all;use ieee

std_logic_arith

all;use ieee

std_logic_unsigned

all;entity count10 isport (clk:in std_logic; f:buffer integer range 0 to 15; cout:out std_logic); end;architecture aa of count10 isbeginprocess(clk)begin if falling_edge(clk) thenif f=9 thenf