JCPKSDRDQQSDRDDCPQQ43121556423156实验三:基本门电路及触发器实 验 室:实验台号:日期:专业班级:姓名:学号:一、实验目的1

了解 TTL 门电路的原理,性能好使用方法,验证基本门电路逻辑功能

掌握门电路的设计方法

验证 J-K 触发器的逻辑功能

掌握触发器转换的设计方法

二、实验内容(一)验证以下门电路的逻辑关系1

用与非门( 00)实现与门逻辑关系: F=AB 2

异或门( 86):(二):门电路的设计 (二选一 ) 1

用 74LS00 和 74LS86 设计半加器

用 TTL 与非门设计一个三人表决电路

A B C 三个裁判,当表决某个提案时,多数人同意提案为通过

(1 为同意, 0 为不同意)要求:用 74LS00 和 74LS10 芯片

(三)验证 JK 触发器的逻辑关系1.J-K 触发器置位端、复位端及功能测试

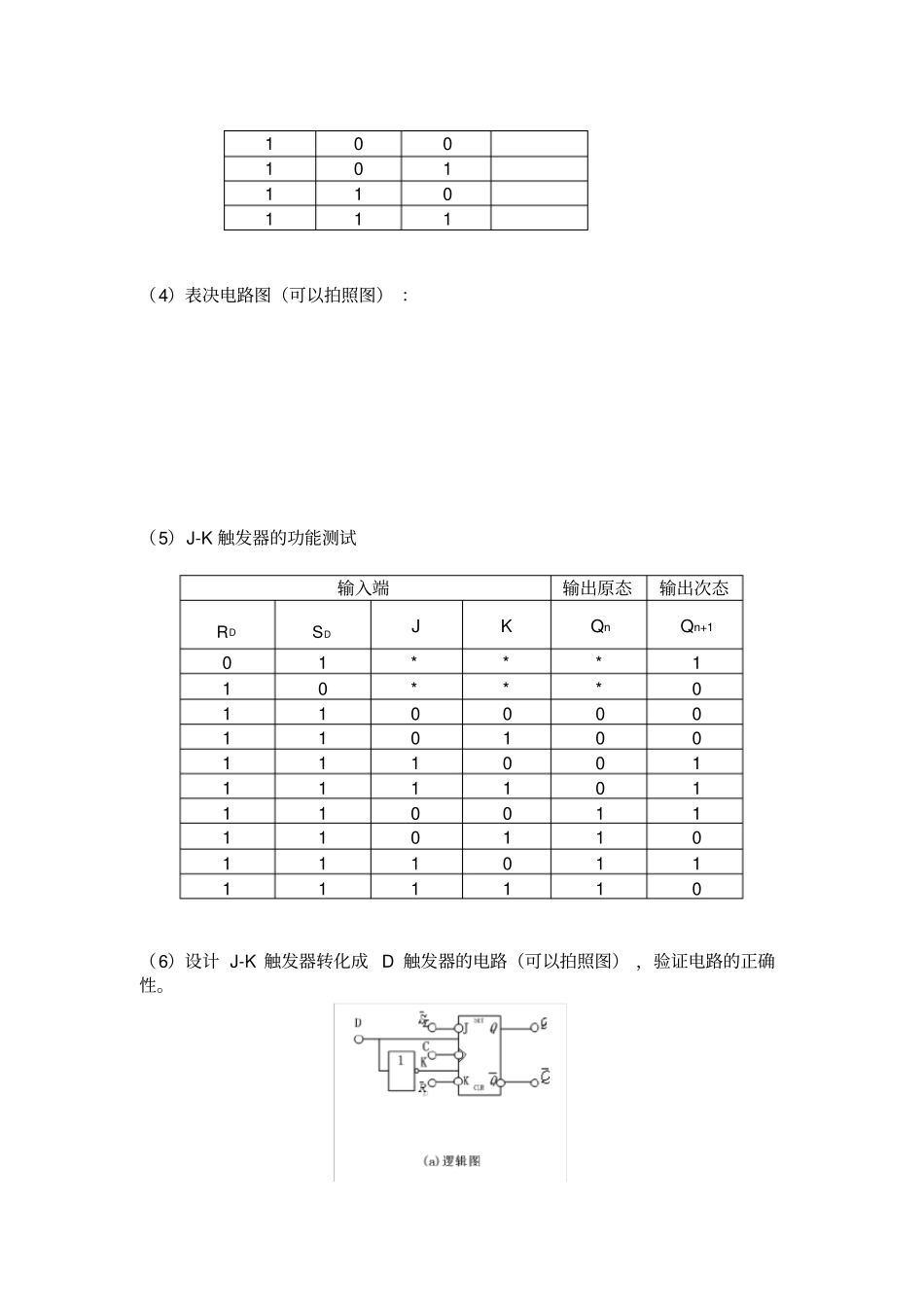

图 3-1 JK 触发器 (74LS112)和 D 触发器 (74LS74) 2、设计 J-K 触发器转化成 D 触发器的电路利用与非门和 J-K 触发器设计并测试逻辑功能

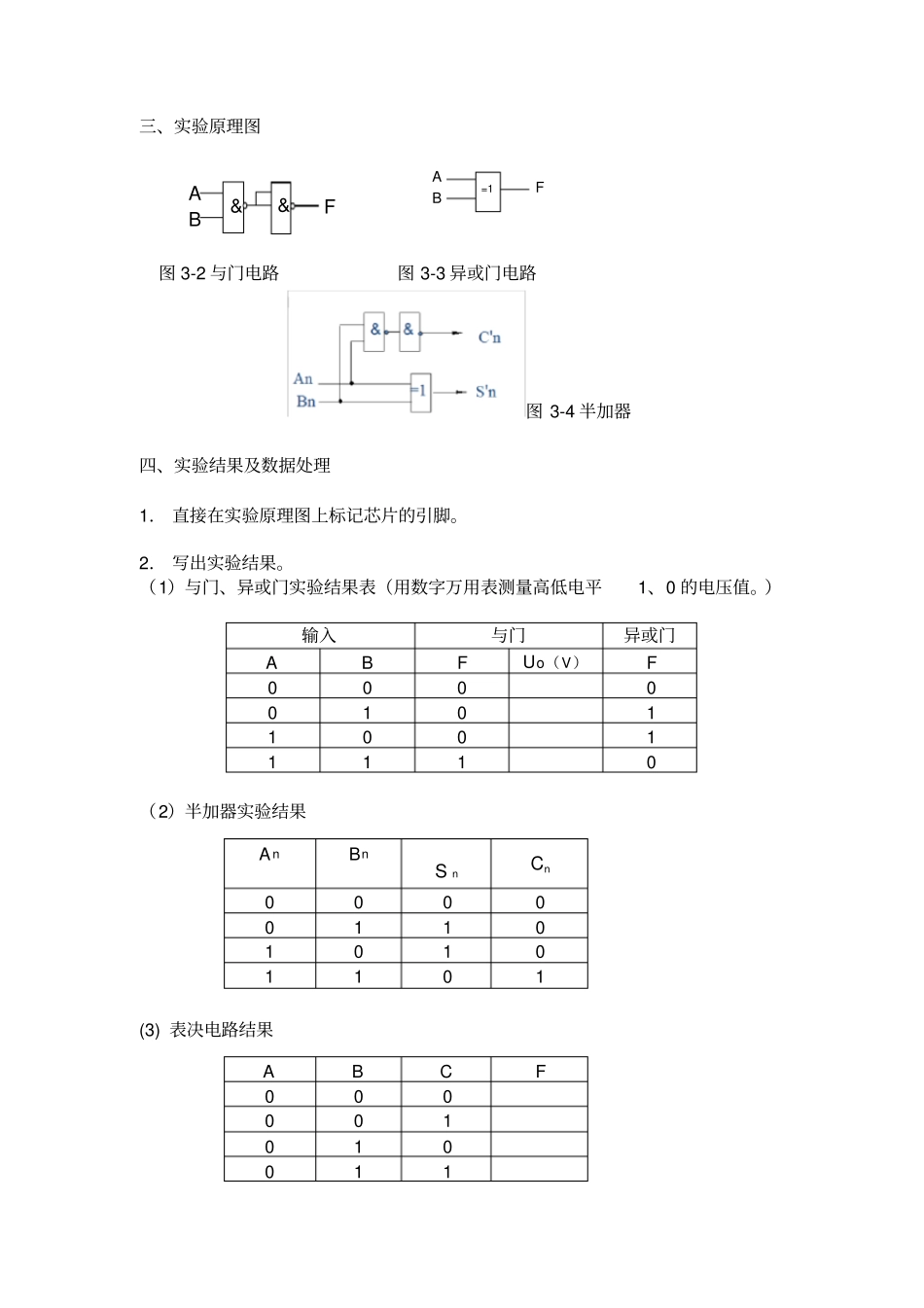

BABABAFnnnnnnnBABABAS'nnnBAC'&AB&F三、实验原理图图 3-2 与门电路图 3-3 异或门电路图 3-4 半加器四、实验结果及数据处理1. 直接在实验原理图上标记芯片的引脚

2. 写出实验结果

(1)与门、异或门实验结果表(用数字万用表测量高低电平1、0 的电压值

)输入与门异或门A B F Uo(V)F 0 0 0 0 0 1 0 1 1 0 0 1 1 1 1 0 (2)半加器实验结果(3) 表决电路结果A nBnnSnC0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 1 A B C F 0 0 0 0 0 1 0 1 0 0 1 1 =1ABF(4)表决电路图(可以拍照图) :(