P CIE 3

0 简介及信号和协议测试方法 安捷伦科技(中国)有限公司:李凯 一、前言 PCI Express(简称 PCIE)总线是 PCI 总线的串行版本,其采用多对高速串行的差分信号进行高速传输,每对差分线上的信号速率可以是 1 代的 2

5Gbps、2 代的5Gbps 以及现在正逐渐开始应用的 3 代 8Gbps

PCIE 标准是由 PCI-SIG 组织制定,自从推出以来,1 代和2 代标准已经在 PC 和Server 上逐渐普及,用于支持高速显卡以及其它接口卡对于高速数据传输的要求

出于支持更高总线数据吞吐率的目的,PCI-SIG 组织在 2010 年制定了 PCIE 3

0,即PCIE 3 代的规范

目前,PCIE 3

0 已经开始出现在一些高端的 Server 上,而在普通PC 上的应用也是指日可待

那么 PCIE 3

0 总线究竟有什么特点

对于其测试有什么特殊的地方呢

我们这里就来探讨一下

二、PCIE 3

0 简介 1、信号速率的变化 首先我们看一下制定 PCIE 3 代规范的目的,其目的主要是要在现有的 FR4 板材和接插件的基础上提供比 PCIE 2 代高一倍的有效数据传输速率,同时保持和原有 1 代、2 代设备的兼容

别看这是个简单的目的,但实现起来可不容易

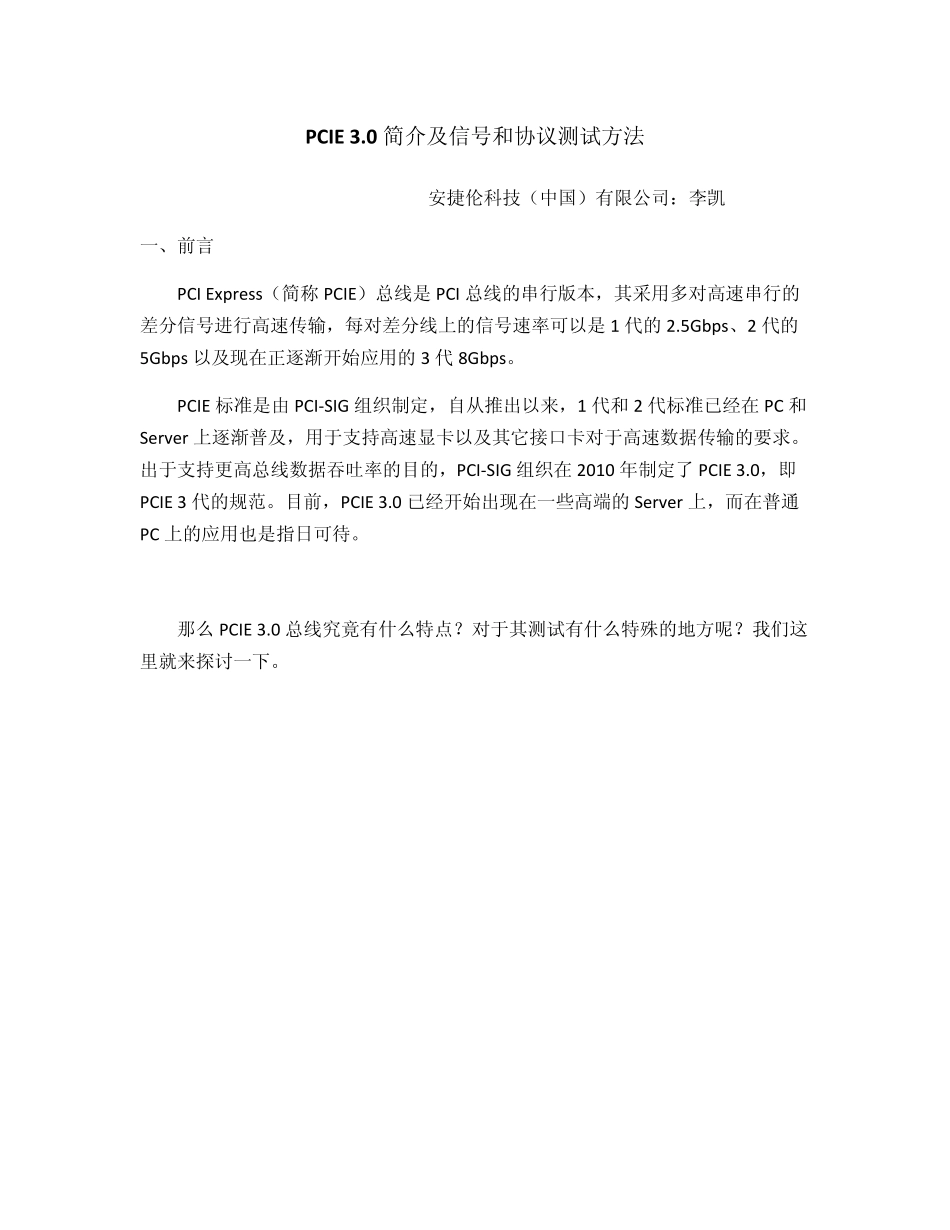

我们知道,PCIE 2 代在每对差分线上的数据传输速率是 5Gbps,相对于 1 代提高了 1 倍;而 3 代要相对于 2 代把速率也提高一倍,理所当然的是把数据传输速率提高到 10Gbps

但是就是这个 10Gbps 把 PCI-SIG 给难住了,因为 PC 和 Server上出于成本的考虑,普遍使用便宜的 FR4 的 PCB 板材以及廉价的接插件,无论采用什么技术都很难保证 10Gbps 的信号还能在原来的信号路径上可靠地传输很远的距离(典型距离是 15~30cm)

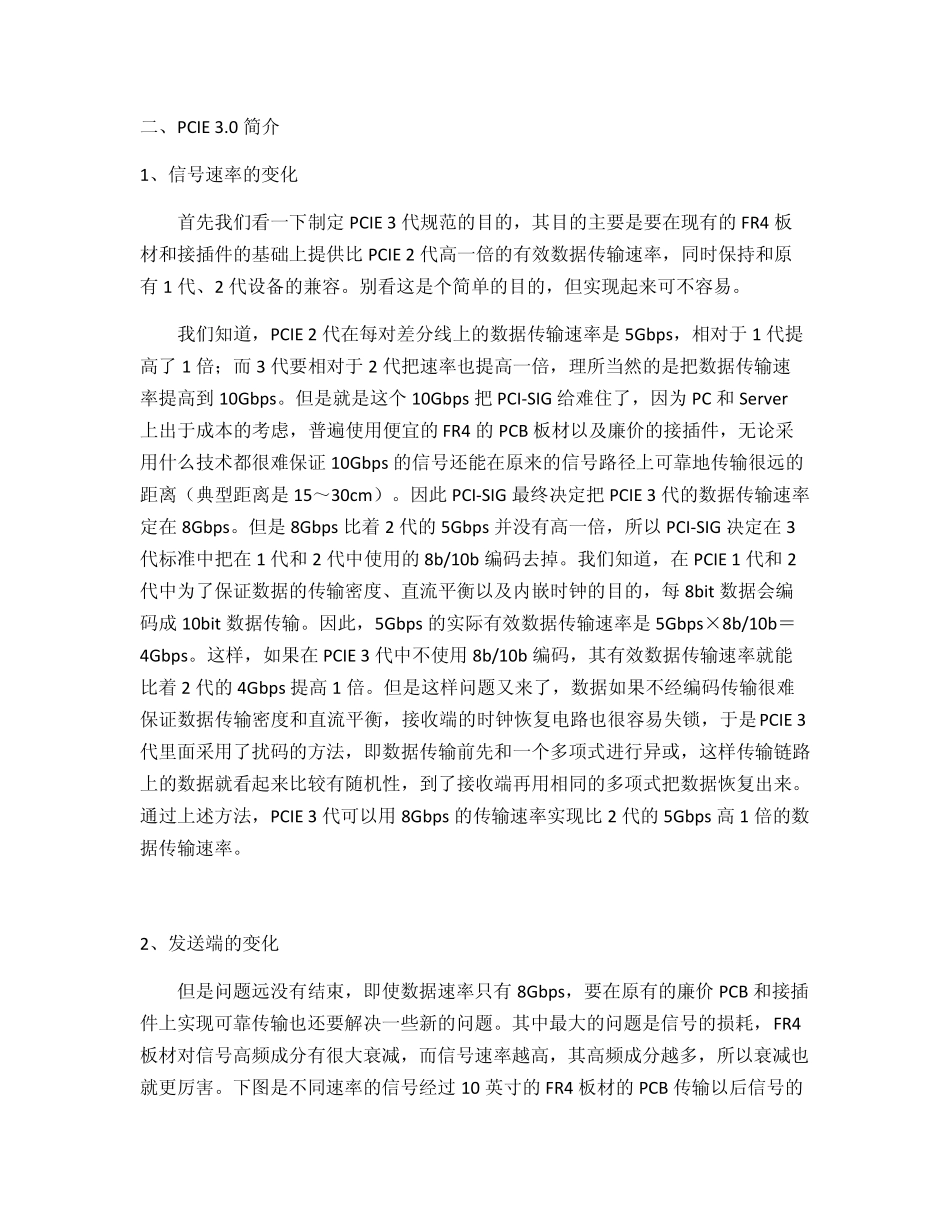

因此PCI-