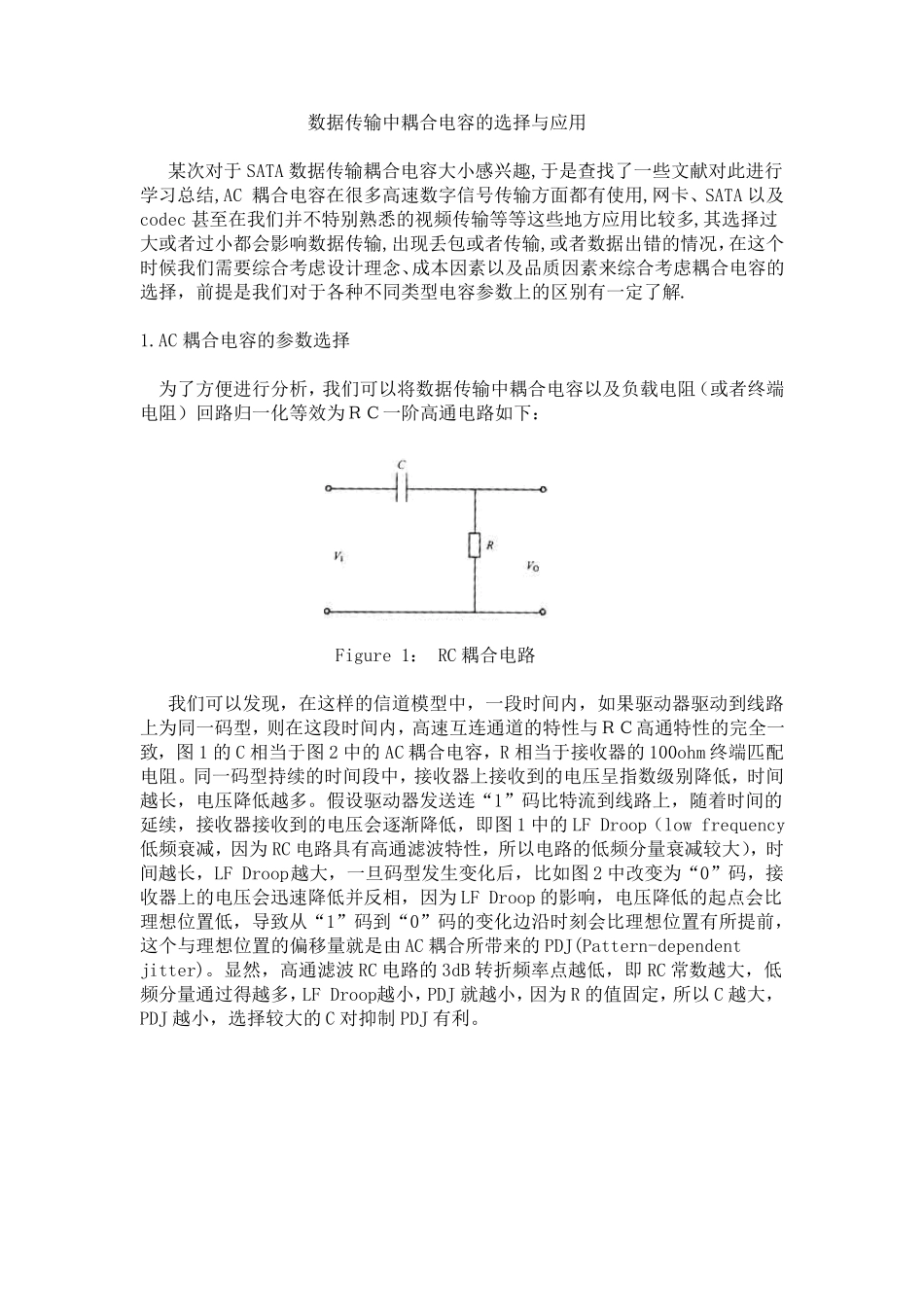

数据传输中耦合电容的选择与应用 某次对于SATA 数据传输耦合电容大小感兴趣,于是查找了一些文献对此进行学习总结,AC 耦合电容在很多高速数字信号传输方面都有使用,网卡、SATA 以及codec 甚至在我们并不特别熟悉的视频传输等等这些地方应用比较多,其选择过大或者过小都会影响数据传输,出现丢包或者传输,或者数据出错的情况,在这个时候我们需要综合考虑设计理念、成本因素以及品质因素来综合考虑耦合电容的选择,前提是我们对于各种不同类型电容参数上的区别有一定了解. 1.AC 耦合电容的参数选择 为了方便进行分析,我们可以将数据传输中耦合电容以及负载电阻(或者终端电阻)回路归一化等效为RC一阶高通电路如下: Figure 1: RC 耦合电路 我们可以发现,在这样的信道模型中,一段时间内,如果驱动器驱动到线路上为同一码型,则在这段时间内,高速互连通道的特性与RC高通特性的完全一致,图 1 的C 相当于图 2 中的AC 耦合电容,R 相当于接收器的100ohm 终端匹配电阻。同一码型持续的时间段中,接收器上接收到的电压呈指数级别降低,时间越长,电压降低越多。假设驱动器发送连“1”码比特流到线路上,随着时间的延续,接收器接收到的电压会逐渐降低,即图 1 中的LF Droop(low frequency低频衰减,因为 RC 电路具有高通滤波特性,所以电路的低频分量衰减较大),时间越长,LF Droop越大,一旦码型发生变化后,比如图 2 中改变为“0”码,接收器上的电压会迅速降低并反相,因为 LF Droop 的影响,电压降低的起点会比理想位置低,导致从“1”码到“0”码的变化边沿时刻会比理想位置有所提前,这个与理想位置的偏移量就是由 AC 耦合所带来的PDJ(Pattern-dependent jitter)。显然,高通滤波 RC 电路的3dB 转折频率点越低,即 RC 常数越大,低频分量通过得越多,LF Droop越小,PDJ 就越小,因为 R 的值固定,所以 C 越大,PDJ 越小,选择较大的C 对抑制 PDJ 有利。 Figure 2:由AC 耦合产生的LF Droop 和PDJ 图示说明: 上图为中粗实线表示比较长的0 或者1 的码型,虚线表示正常的最高频率进行数据传输的时候码型,这个图的意思是长时间为1 的时候导致的电平降低。 根据经典的RC 一阶电压的阶跃响应公式 设接收端上的初始电压(也就是加在R 上的初始电压)为“1”码和“0”码电平的中间值0.5VPP,我们可以得到以下公式: 其中△V为电压衰减,假设电压的衰减△V/Vpp 为6%。有...