彻底理解锁存器,让你不再为锁存器头疼

锁存器(latch):是电平触发的存储单元,数据存储的动作(状态转换)取决于输入时钟(或者使能)信号的电平值,尽当锁存器处于使能状态时,输出才会随着数据输入发生变化

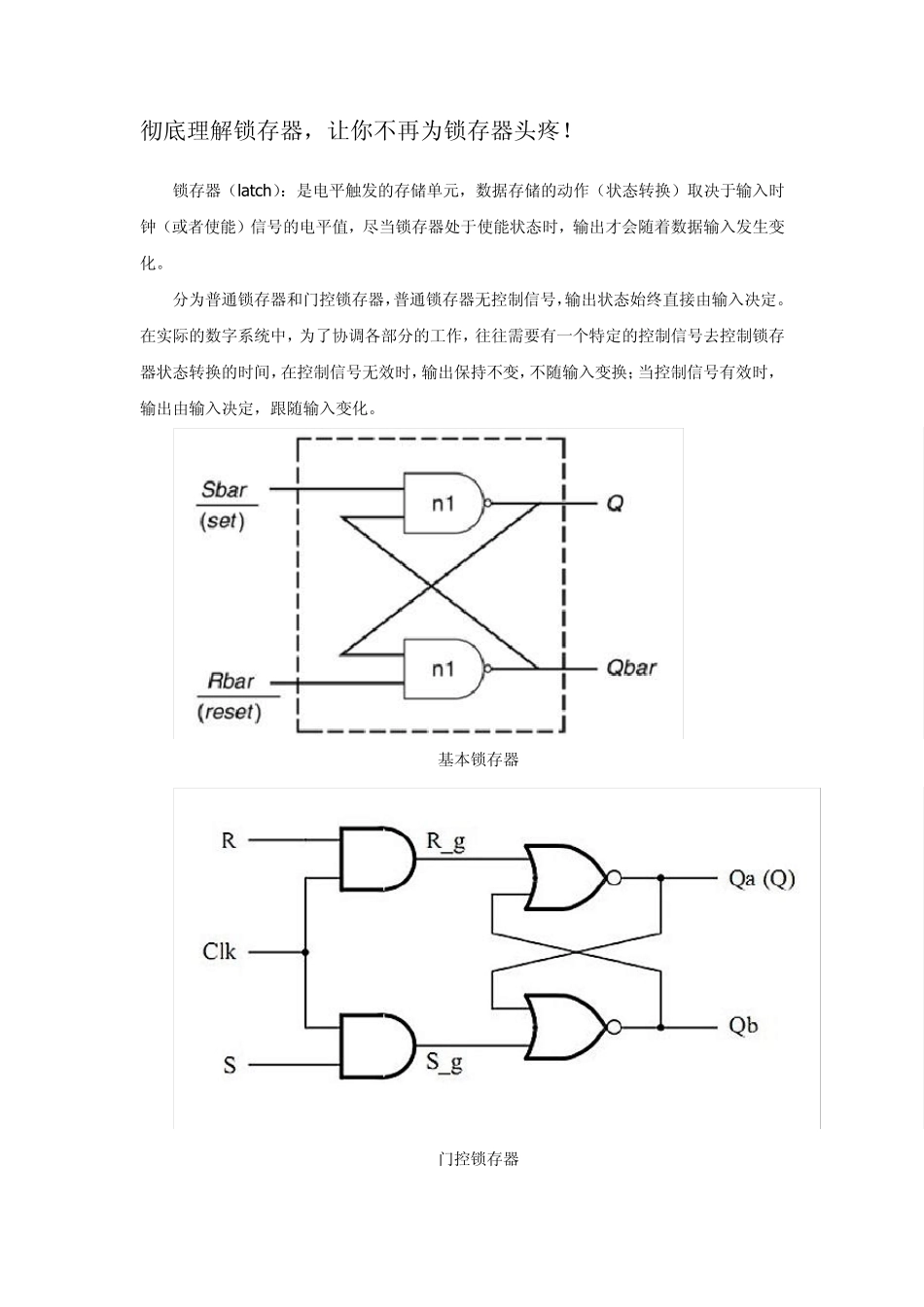

分为普通锁存器和门控锁存器,普通锁存器无控制信号,输出状态始终直接由输入决定

在实际的数字系统中,为了协调各部分的工作,往往需要有一个特定的控制信号去控制锁存器状态转换的时间,在控制信号无效时,输出保持不变,不随输入变换;当控制信号有效时,输出由输入决定,跟随输入变化

基本锁存器 门控锁存器 ①正是因为门控锁存器在控制信号有效的期间内,都可以接收输入信号,所以,激励信号的任何变化,都将直接引起锁存器输出状态的改变

这时输入信号若发生多次变化,输出状态也可能发生多次变化,这一现象称为锁存器的空翻

②其次,当门控锁存器的控制信号有效时,锁存器就变成了一个组合电路,时序逻辑电路的模型就等效为两个各组合电路互为反馈的反馈系统,因此,系统有可能会因为瞬态特性不稳定而产生振荡现象

触发器(flip-flop)是边沿敏感的存储单元,数据存储的动作(状态转换)由某一信号的上升或者下降沿进行同步的(限制存储单元状态转换在一个很短的时间内)

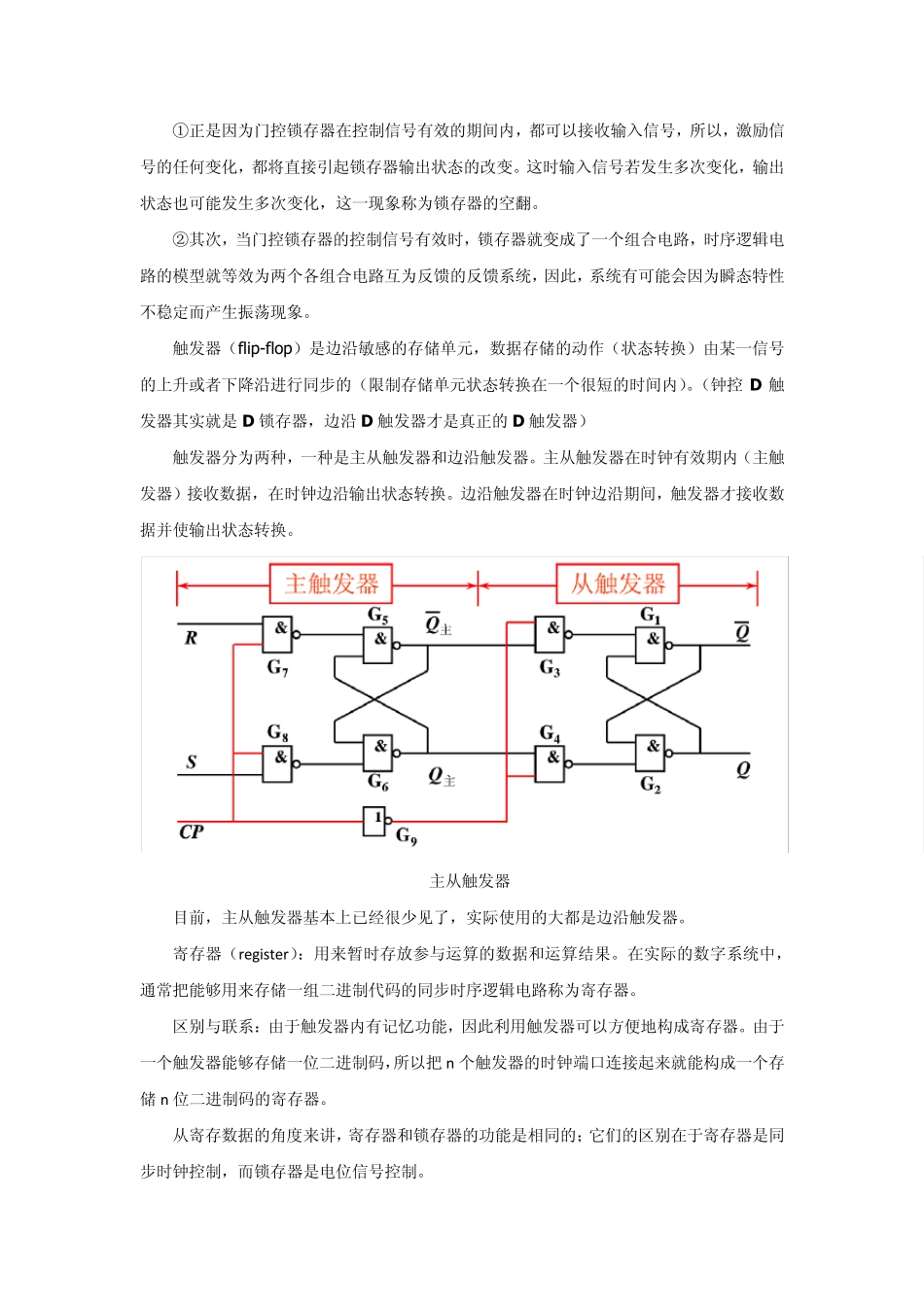

(钟控 D 触发器其实就是 D 锁存器,边沿 D 触发器才是真正的 D 触发器) 触发器分为两种,一种是主从触发器和边沿触发器

主从触发器在时钟有效期内(主触发器)接收数据,在时钟边沿输出状态转换

边沿触发器在时钟边沿期间,触发器才接收数据并使输出状态转换

主从触发器 目前,主从触发器基本上已经很少见了,实际使用的大都是边沿触发器

寄存器(register):用来暂时存放参与运算的数据和运算结果

在实际的数字系统中,通常把能够用来存储一组二进制代码的同步时序逻辑电路称为寄存器

区别与联系:由于触发器内有记忆功能,因此利用触发器可以方便地构成