SDRAM 工作原理和S3C2410 SDRAM 扩展控制器配置方法 SDRAM 的工作原理、控制时序、及相关控制器的配置方法一直是嵌入式系统学习、开发过程中的一个难点

掌握 SDRAM 的知识对硬件设计、编写系统启动代码、提高系统存取效率、电源管理都有一定的意义

本文想通过: 1

SDRAM 的工作原理

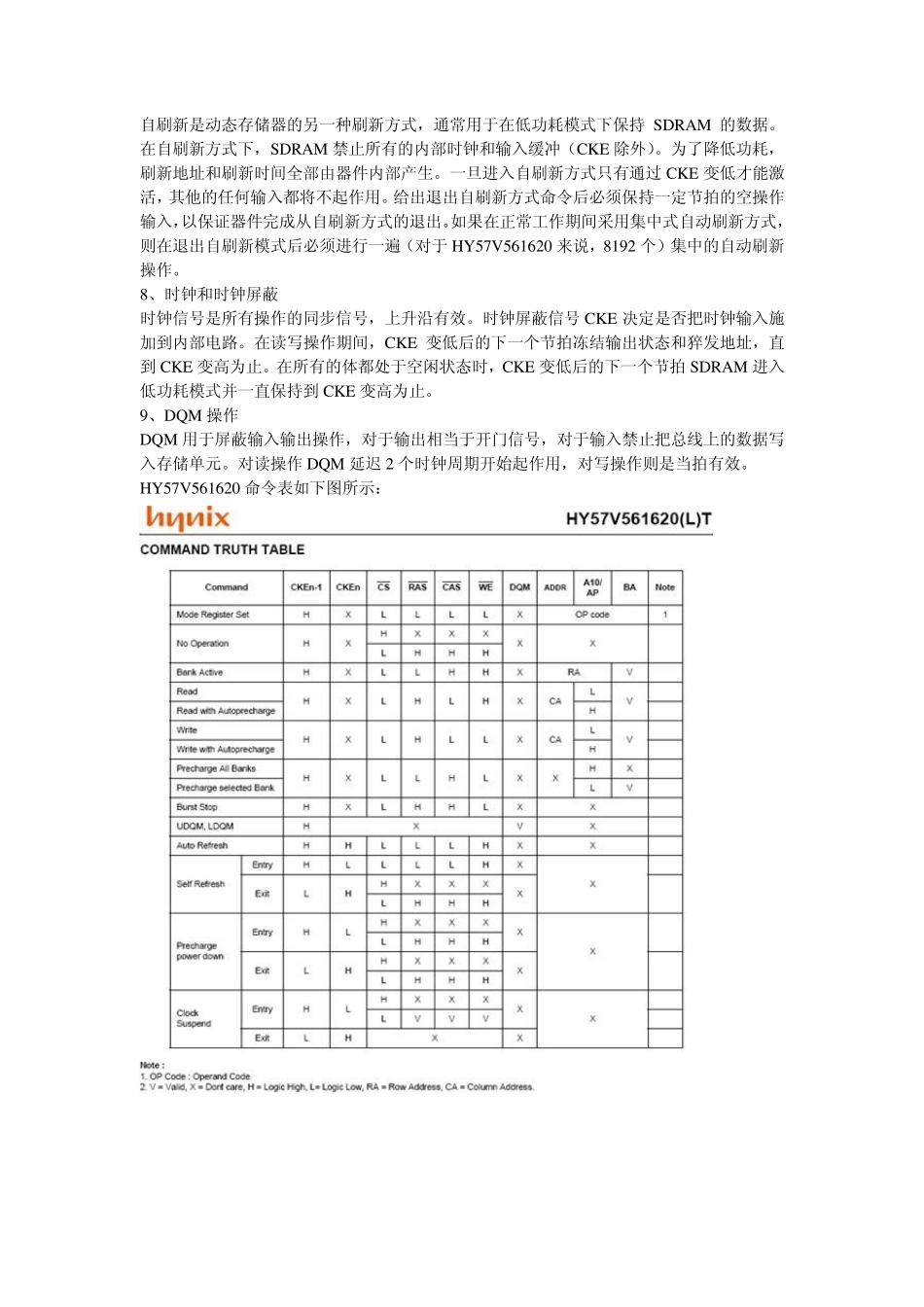

HY57V561620 SDRAM 介绍

S3C2410 和HY57V561620 的接线方法

S3C2410 SDRAM 控制器的配置方法

SDRAM 控制时序分析 这 5 个方面来帮助初学者了解 SDRAM

一、SDRAM 的工作原理 SDRAM 之所以成为 DRARM 就是因为它要不断进行刷新(Refresh)才能保留住数据,因此它是 DRAM 最重要的操作

那么要隔多长时间重复一次刷新呢

目前公认的标准是,存储体中电容的数据有效保存期上限是 64ms(毫秒,1/1000 秒),也就是说每一行刷新的循环周期是 64ms

这样刷新速度就是:行数量/64ms

我们在看内存规格时,经常会看到 4096 Refresh Cycles/64ms 或 8192 Refresh Cycles/64ms 的标识,这里的4096 与 8192 就代表这个芯片中每个 Bank 的行数

刷新命令一次对一行有效,发送间隔也是随总行数而变化,4096 行时为 15

625μs(微秒,1/1000 毫秒),8192 行时就为 7

8125μs

HY57V561620 为 8192 refresh cycles / 64ms

SDRAM 是多 Bank 结构,例如在一个具有两个 Bank 的SDRAM 的模组中,其中一个 Bank在进行预充电期间,另一个 Bank 却马上可以被读取,这样当进行一次读取后,又马上去读取已经预充电 Bank 的数据时,就无需等待而是可以