2009 级数字电路实验报告 实验名称: EDA 基础实验 学生姓名: 桂柯易 班 级: 2009211120 班内序号: 07 学 号: 09210580 日 期: 2011 年4 月28 日 1

实验要求 【实验目的】 1

熟悉用QuartusII原理图输入法进行电路设计和仿真; 2

掌握QuartusII图形模块单元的生成与调用; 3

熟悉用VHDL语言设计组合逻辑电路和时序电路的方法; 4

熟悉用QuartusII文本输入法和图形输入法进行电路设计; 5

熟悉不同的编码及其之间的转换; 6

掌握触发器的逻辑功能及使用方法; 7

熟悉计数器、寄存器、锁存器、分频器、移位寄存器的设计方法 8

掌握VHDL语言的语法规范,掌握时序电路描述方法; 9

掌握多个数码管动态扫描显示的原理及设计方法

【实验所用仪器及元器件】 1

直流稳压电源 3

数字系统与逻辑设计实验开发板 【实验内容】 1

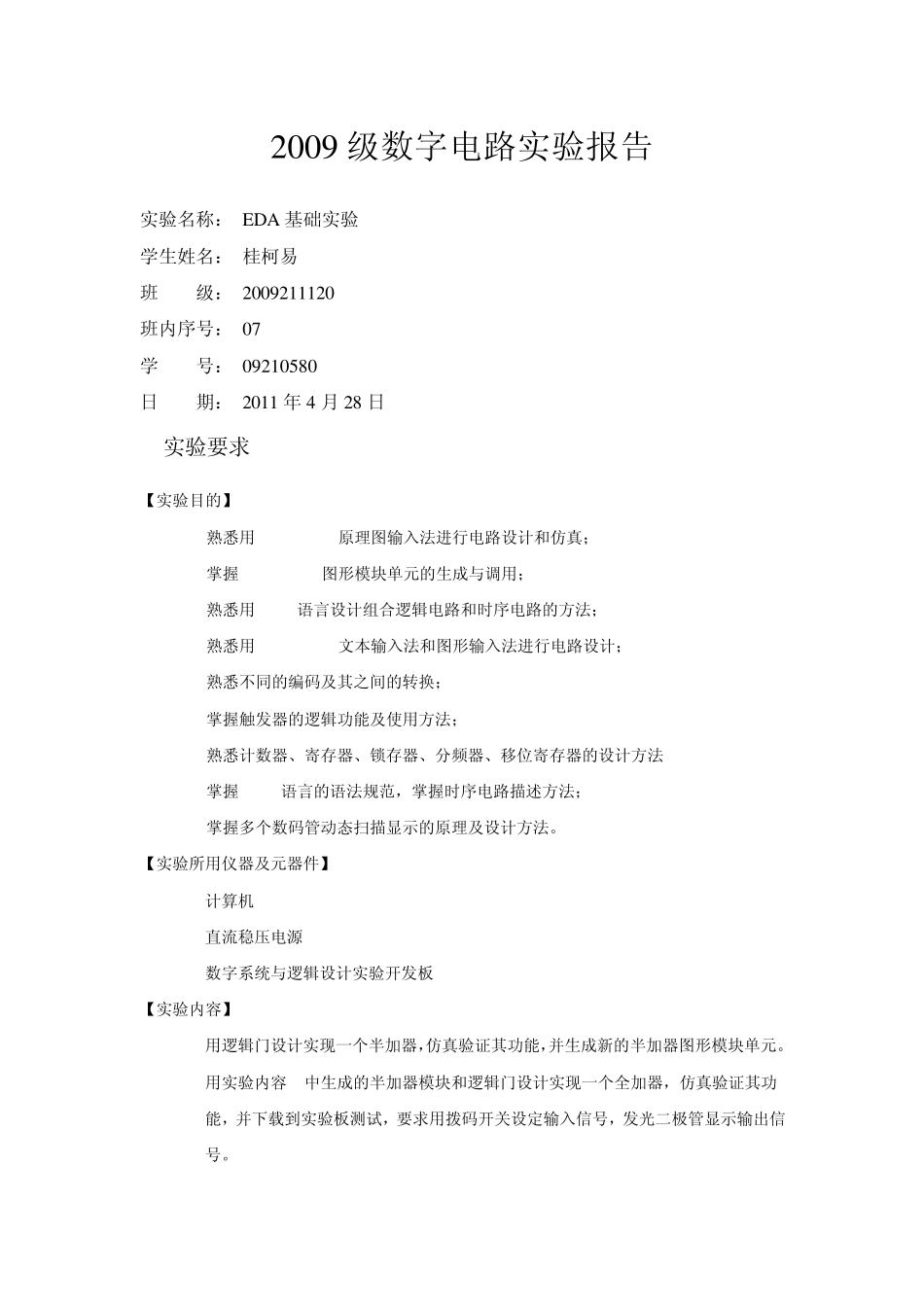

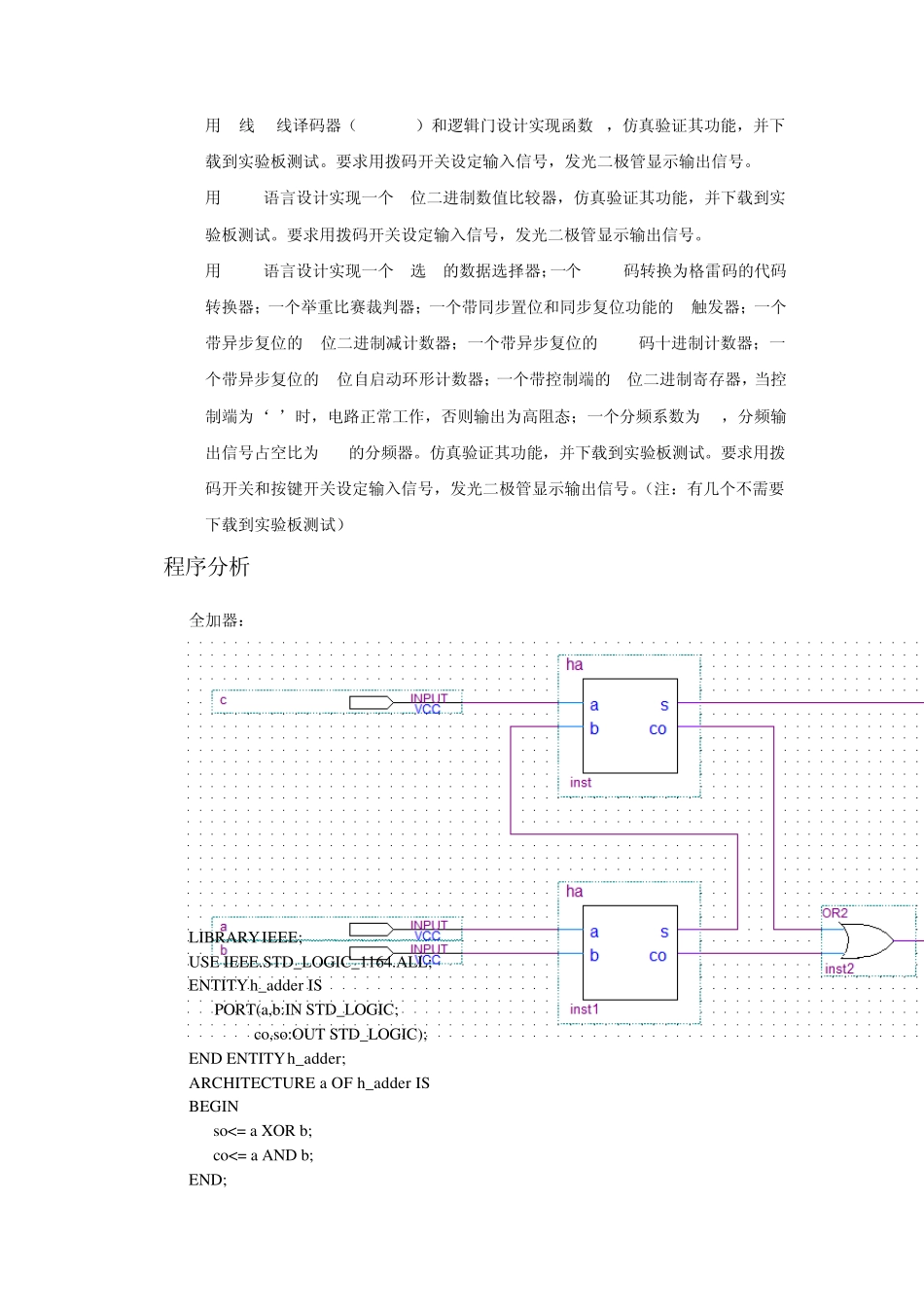

用逻辑门设计实现一个半加器,仿真验证其功能,并生成新的半加器图形模块单元

用实验内容 1中生成的半加器模块和逻辑门设计实现一个全加器,仿真验证其功 能,并下载到实验板测试,要求用拨码开关设定输入信号,发光二极管显示输出信 号

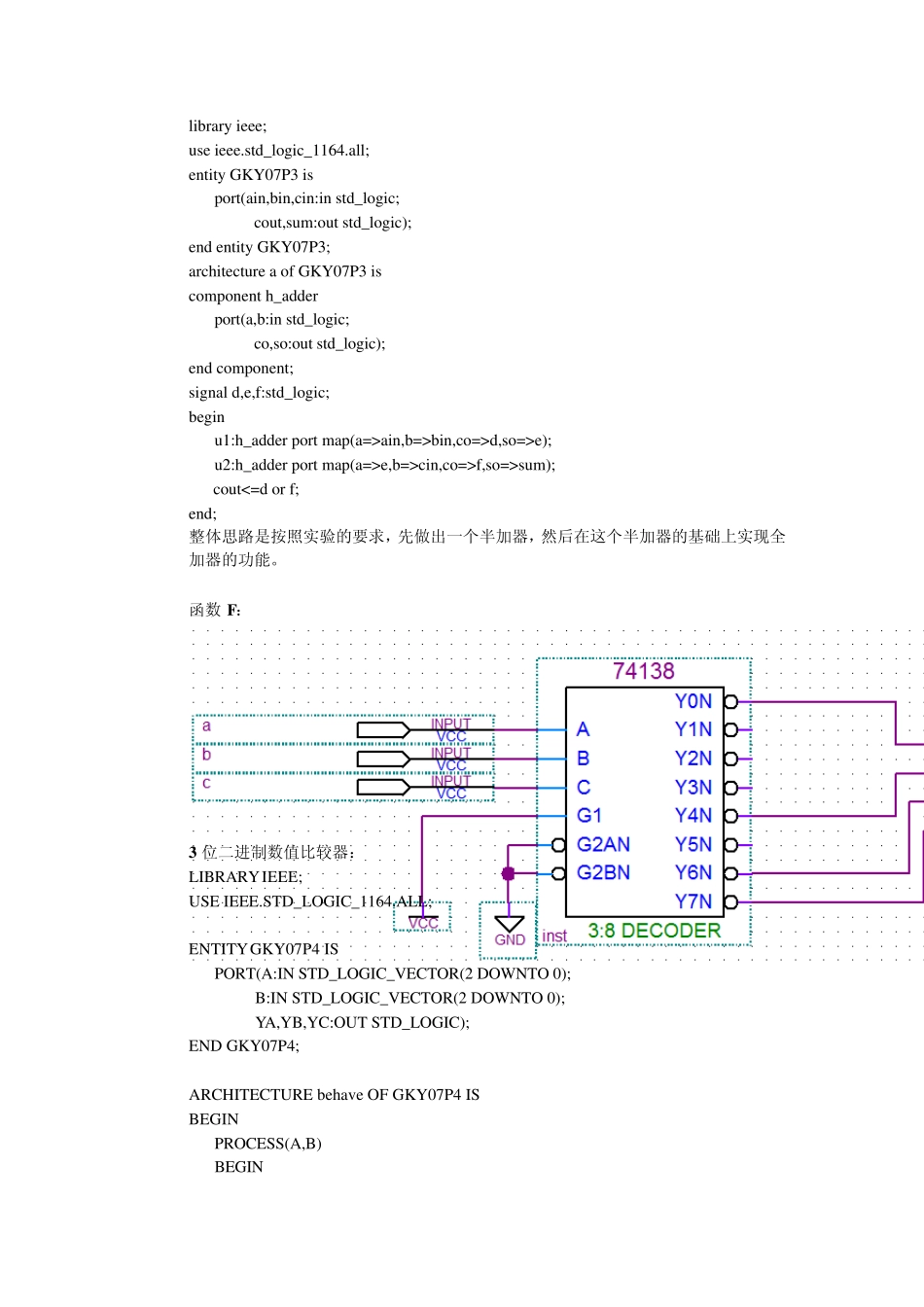

用3线-8线译码器(74LS138)和逻辑门设计实现函数F,仿真验证其功能,并下 载到实验板测试

要求用拨码开关设定输入信号,发光二极管显示输出信号

用VHDL语言设计实现一个3位二进制数值比较器,仿真验证其功能,并下载到实 验板测试

要求用拨码开关设定输入信号,发光二极管显示输出信号

用VHDL语言设计实现一个4选1的数据选择器;一个8421码转换为格雷码的代码 转换器;一个举重比赛裁判器;一个带同步置位和同步复位功能的D触发器;一个 带异步复位的4位二进制减计数器;一个带异步复位的8421码十进制计数器;一 个带异步复位的4位