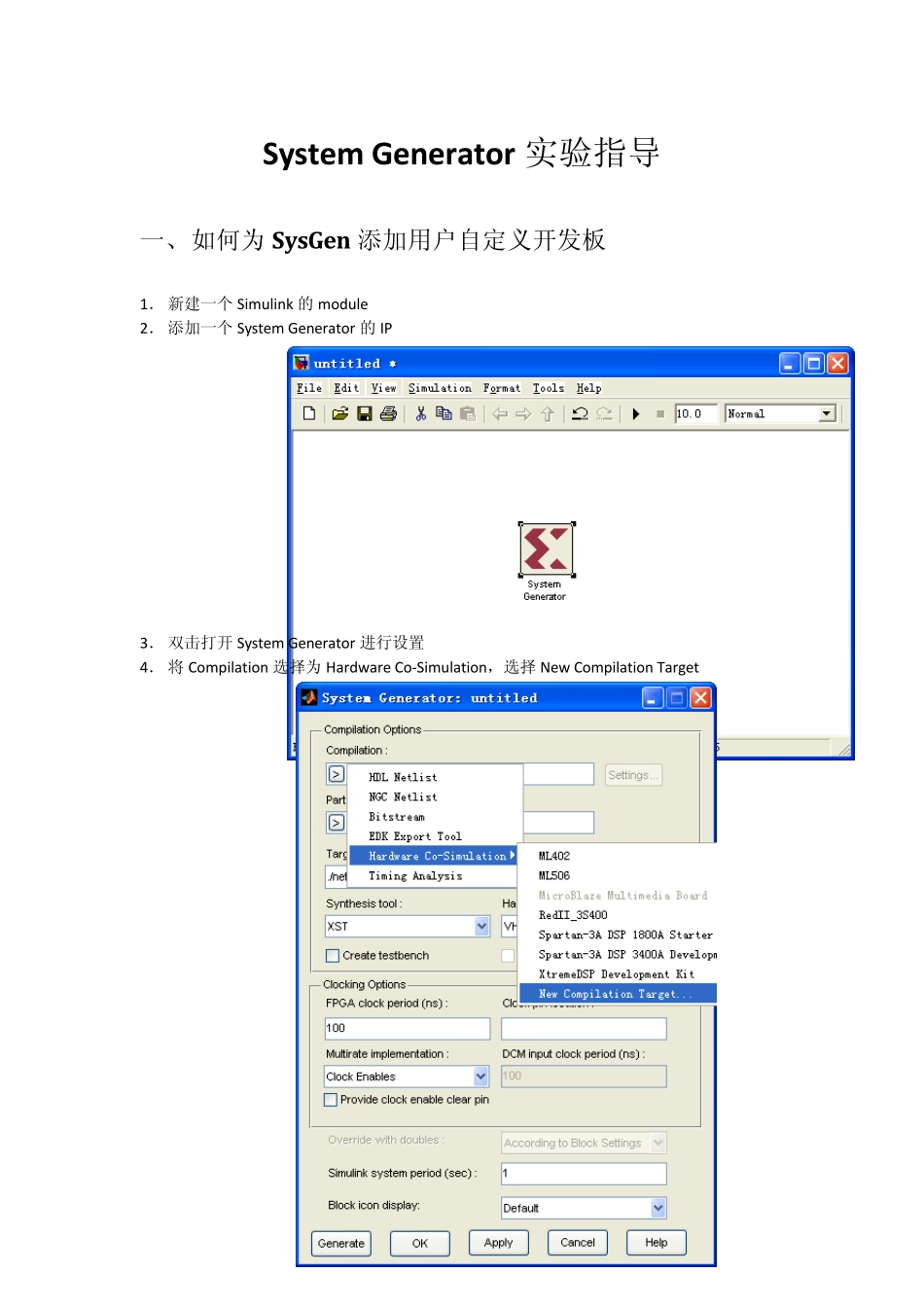

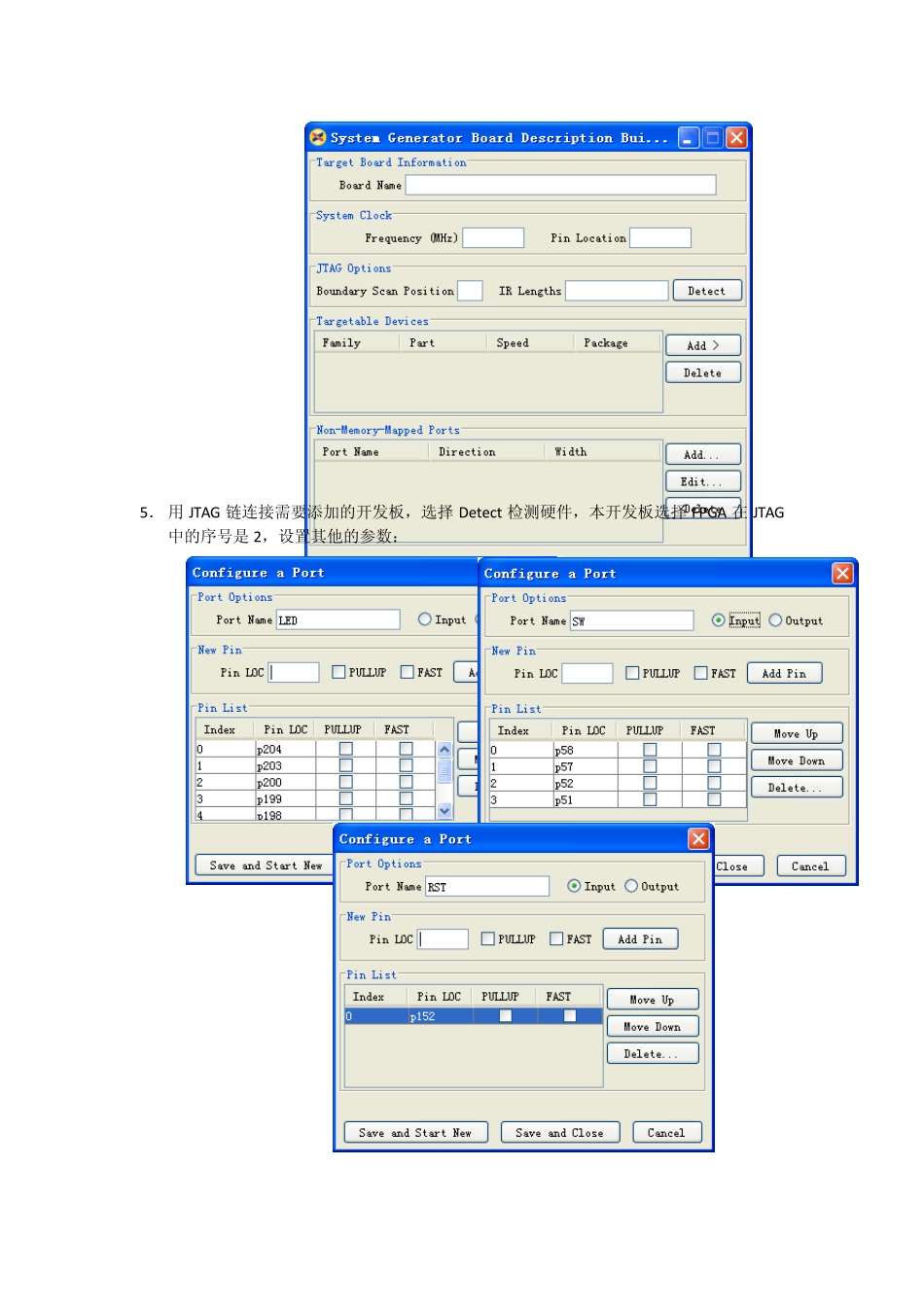

System Generator 实验指导 一、 如何为 SysGen 添加用户自定义开发板 1. 新建一个 Simulink 的 module 2. 添加一个 System Generator 的 IP 3. 双击打开 System Generator 进行设置 4. 将 Compilation 选择为 Hardware Co-Simulation,选择 New Compilation Target… 5. 用JTAG 链连接需要添加的开发板,选择Detect检测硬件,本开发板选择FPGA 在JTAG中的序号是 2,设置其他的参数: 选择Save Zip 并且Install: 保存并选择Install 后,将在如下目录生成该开发板的信息: 同时,生成相应的外围组建模块: 保存该外围组建模块

System Generator 将在下次选择Hardware Co-Simulation 时发现此新硬件: 二、 硬件在环测试 HIL 演示 1.Matlab 工作目录设置: 2.新建一个 Simulink 的 module,保存在该目录,文件名为 Adder_Netlist

3.添加 System Generator、Gateway In、Gateway Out、Resourse Estimator 和 AddSub 模块

4.添加 Constant 和 Scope 模块

5.设置各模块参数如下: 6.设置System Generator 模块参数如下: 7.选择 Generate 8.生成硬件在环测试模块JTAG Co-sim: 9.打开查看该模块的设置: 10

将该HIL 模块添加至Adder_Netlist 中,运行仿真,可以看到,开发板被编程并且仿真结果正确

三、 在 ISE 工程中调用 SysGen 工程 1

使用 System Generator 生成该