vivado 约束指导手册 时序分析 时序路径 时序路径由设计中instance 之间的连接决定

在数字设计中,时序路径由一对时序元件(sequ ential elements)形成,这对时序元件由一个或二个不同的时钟控制

普通时序路径 在任何设计中最普通的时序路径有以下 4 种: 1 输入端口到内部时序单元路径 2 从时序单元到时序单元之间的内部路径 3 从内部时序单元到输出端口之间的路径 4 输入端口到输出端口之间的路径 输入端口到内部时序单元之间路径 在从输入端口到内部时序单元之间的路径上传输的数据:

通过管脚时钟送出器件

经过一个称为输入延时的延时到达器件端口(SDC 定义)

在到达由目标时钟(destination clock)锁定的时序单元之前须通过器件内部逻辑 从时序单元到时序单元的内部路径 在从时序单元到时序单元的内部路径上传输的数据:

由时序单元发送到器件内部,而此时序单元由源时钟(sou rce clock)驱动

在到达由目标时钟驱动的时序单元之前,须经过一些内部逻辑 内部时序单元到外部端口路径 在从内部时序单元到外部端口路径上的数据:

由时序单元发送到器件内部,而此时序单元由源时钟(sou rce clock)驱动

在到达外部端口之前,须经过一些内部逻辑

在经过一段称为输出延时的额外延时之后被端口时钟捕获(SDC definition) 输入端口到输出端口路径 在从输入端口直接到输出端口的路径上,数据:

不需要在器件内部锁存(latch),直接从输入端口到输出端口

他们通常被称为 In-to-ou t 数据路径

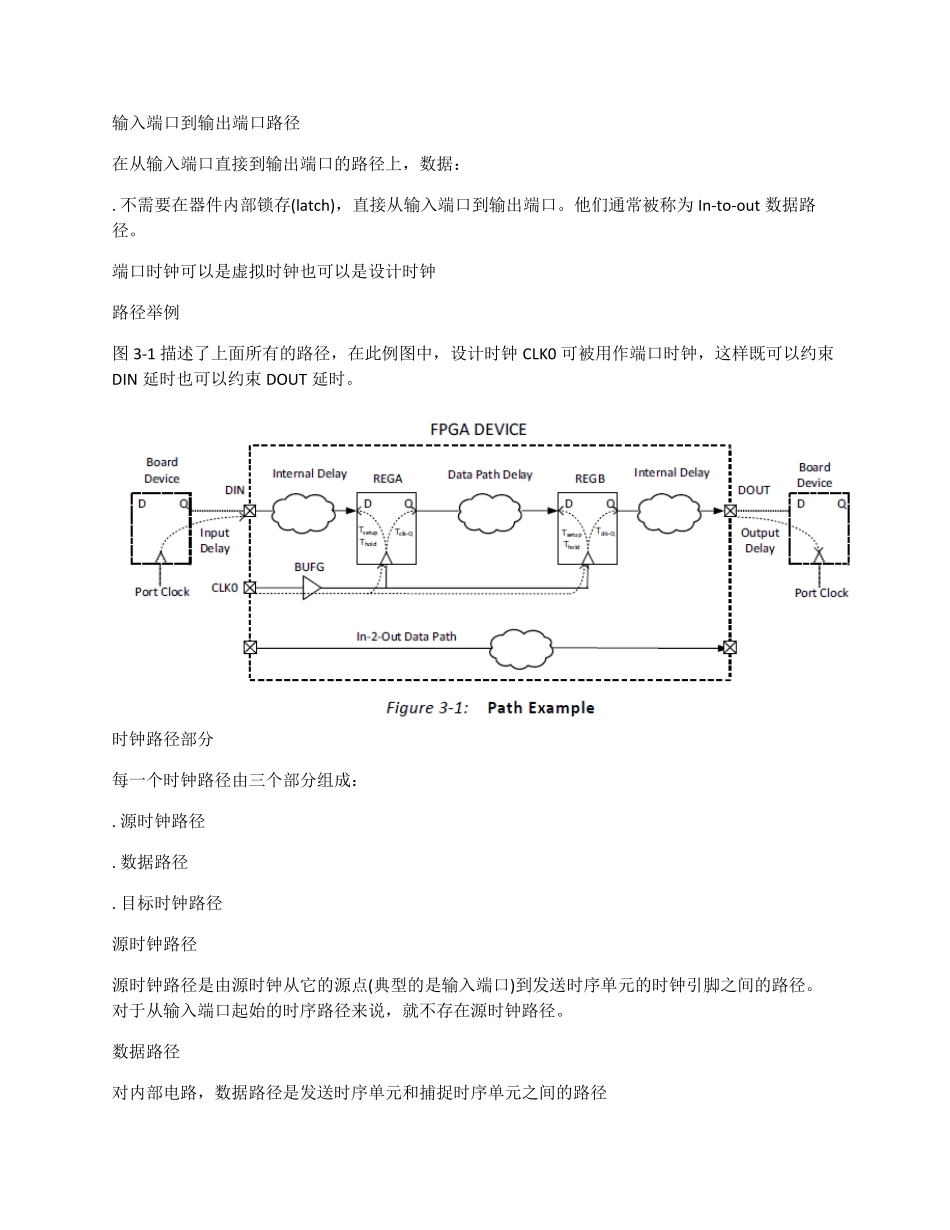

端口时钟可以是虚拟时钟也可以是设计时钟 路径举例 图 3-1 描述了上面所有的路径,在此例图中,设计时钟 CLK0 可被用作端口时钟,这样既可以约束DIN 延时也可以约束 DOUT 延时

时钟路径部分