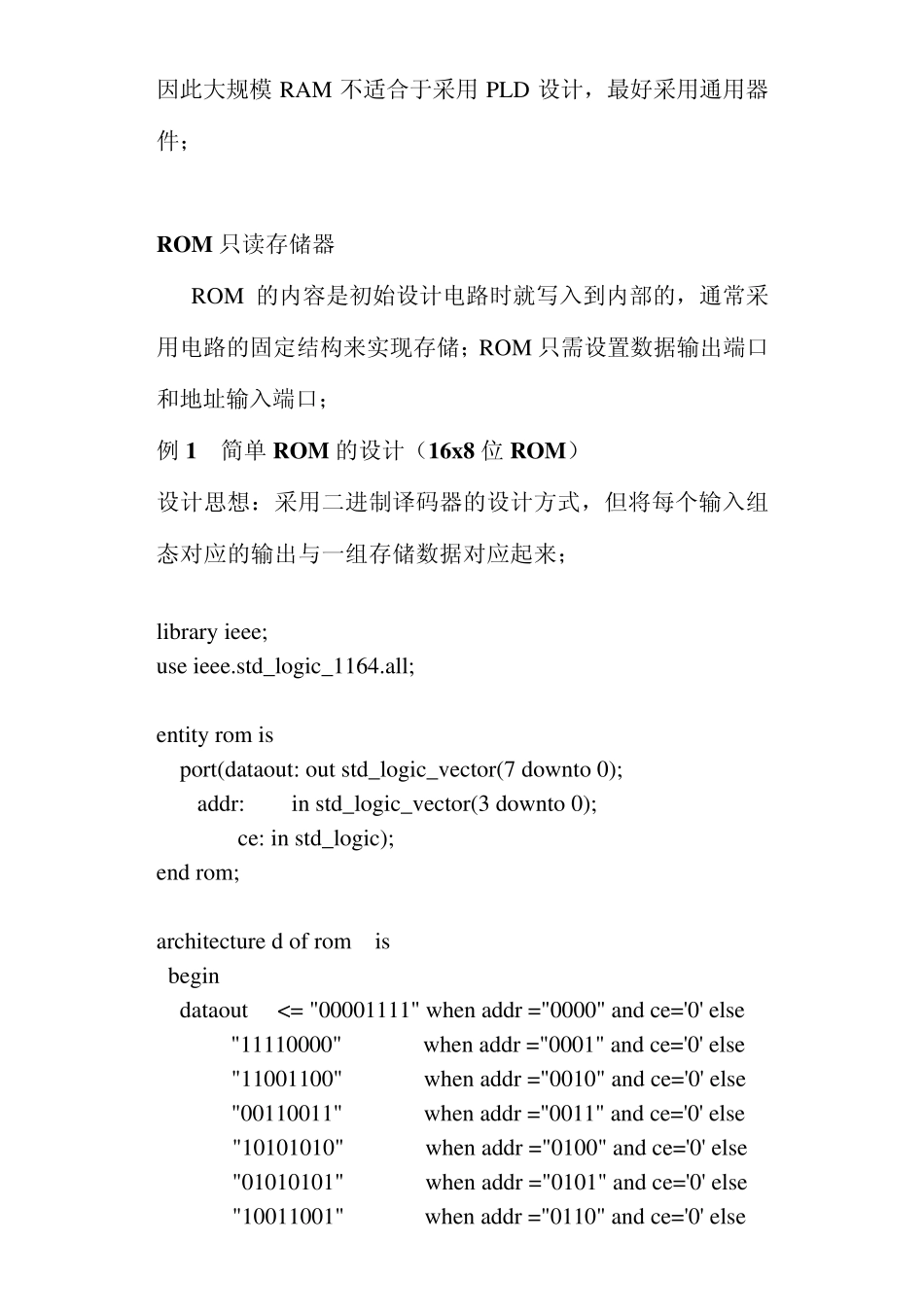

存储器的设计 寻址存储器(RAM 和ROM) ROM 和RAM 属于通用大规模器件,一般不需要自行设计,特别是采用PLD 器件进行设计时; 但是在数字系统中,有时也需要设计一些小型的存储器件,用于特定的用途:临时存放数据,构成查表运算等。 此类器件的特点为地址与存储内容直接对应,设计时将输入地址作为给出输出内容的条件; RAM 随机存储器 RAM 的用途是存储数据,其指标为存储容量和字长; RAM 的内部可以分为地址译码和存储单元两部分; 外部端口为: wr 写读控制 cs 片选 d 数据端口 adr 地址端口 例 16x8 位 RAM 的设计 设计思想: 将每个 8 位数组作为一个字(word);总共存储16 个字; 将 ram 作为由 16 个字构成的数组,以地址为下标; 通过读写控制模式实现对特定地址上字的读出或写入; library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity kram is port ( clk,wr,cs: in std_logic; d: inout std_logic_vector(7 downto 0); adr: in std_logic_vector(3 downto 0)); end kram; architecture beh of kram is subtype word is std_logic_vector(7 downto 0); type memory is array (0 to 15) of word; signal adr_in:integer range 0 to 15; signal sram:memory; begin adr_in<=conv_integer (adr); process(clk) begin if(clk'event and clk='1') then if (cs='1'and wr='1') then sram (adr_in)<=d; end if; if (cs='1'and wr='0' ) then d<=sram (adr_in); end if; end if; end process; end beh; RAM 的数据端口通常为inout 模式,设置仿真输入时只能在写入时将信号加到该输入端口上,在其他时候输入应设置为高阻态; RAM 设计时需要注意器件的大小,一个 16x8 位的RAM大约占用 200 个门,而 256x16 的RAM 则需要 6200 门以上,因此大规模RAM 不适合于采用PLD 设计,最好采用通用器件; ROM 只读存储器 ROM 的内容是初始设计电路时就写入到内部的,通常采用电路的固定结构来实现存储;ROM 只需设置数据输出端口和地址输入端口; 例1 简单ROM 的设计(16x8 位 ROM) 设计思想:采用二进制译码器的设计方式,但将每个输入组态对应的输出与一组存储数据对应起来; library ieee; use ieee.std_logic_1164.all; entity rom is port(da...