VHDL 数字钟设计报告 一

数字钟总体设计方案: 1

1 设计目的 ①正确显示时、分、秒; ②可手动校时,能分别进行时、分的校正; ③整点报时功能; 1

2 设计思路 数字钟的设计模块包括:分频器、去抖动电路、校时电路、“时、分、秒”计数器、校时闪烁电路、整点报时和译码显示电路

每一个功能模块作为一个实体单独进行设计,最后再用 VHDL 的例化语句将各个模块进行整合,生成顶层实体top

该数字钟可以实现 3 个功能:计时功能、设置时间功能和报时功能

二.数字钟模块细节 2

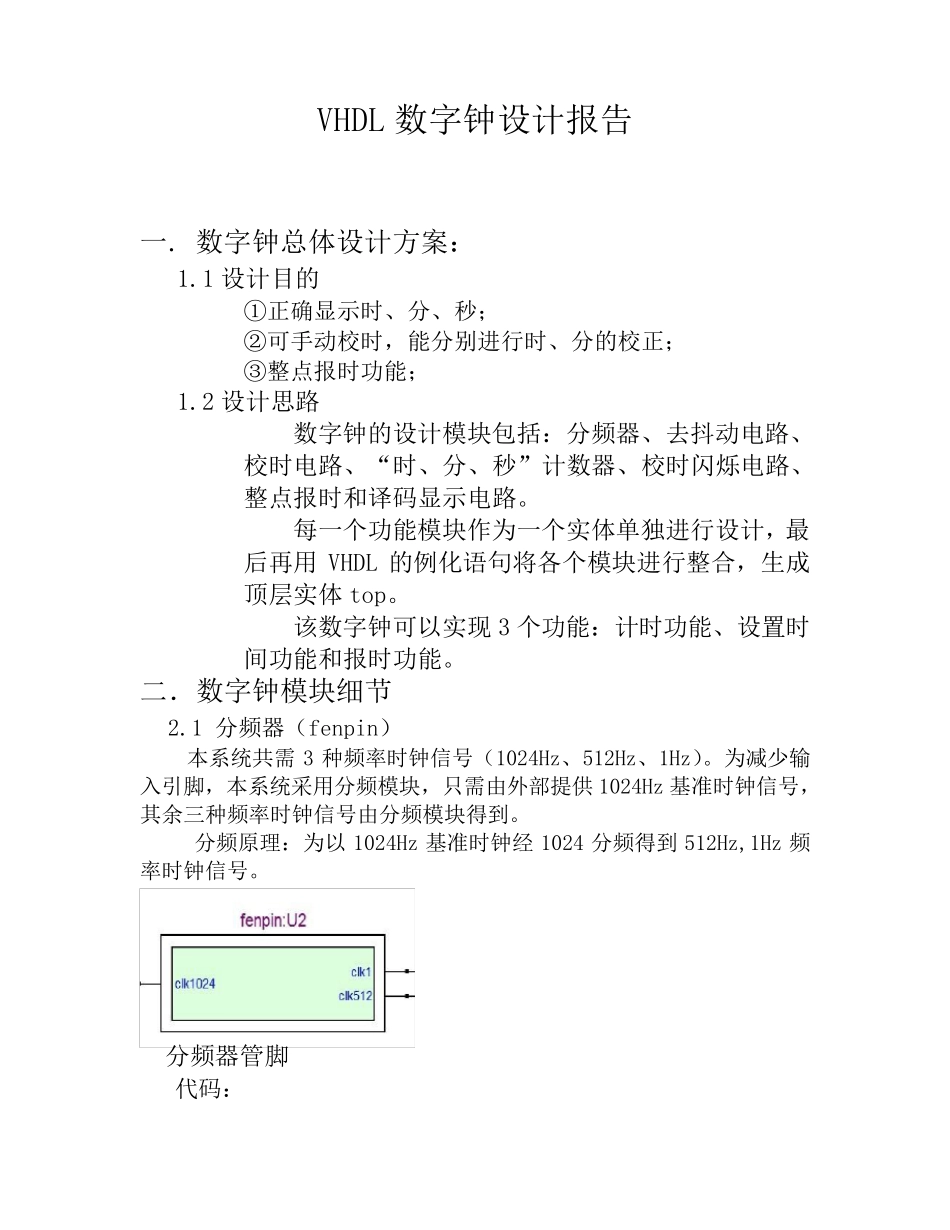

1 分频器(fenpin) 本系统共需 3 种频率时钟信号(1024Hz、512Hz、1Hz)

为减少输入引脚,本系统采用分频模块,只需由外部提供 1024Hz 基准时钟信号,其余三种频率时钟信号由分频模块得到

分频原理:为以 1024Hz 基准时钟经 1024 分频得到 512Hz,1Hz 频率时钟信号

分频器管脚 代码: library ieee; use ieee

std_logic_1164

all; use ieee

std_logic_unsigned

all; use ieee

std_logic_arith

all; entity fenpin is port(clk1024:in std_logic; clk1,clk512:out std_logic ); end fenpin ; architecture cml of fenpin is begin process (clk1024) variable count1: integer range 0 to 512; variable q1: std_logic; begin if clk1024' event and clk1024='1' then if count1=512 then