使用Vivado 制作FPGA 的简要流程一、在 Windows 下安装 XilinxVivado Design Suite:1

XilinxVivado Design Suite 安装文件,解压后得到安装目录:1

运行 xsetup

exe 文件,进入安装程序

如果提示要更新就直接点 continue 关掉

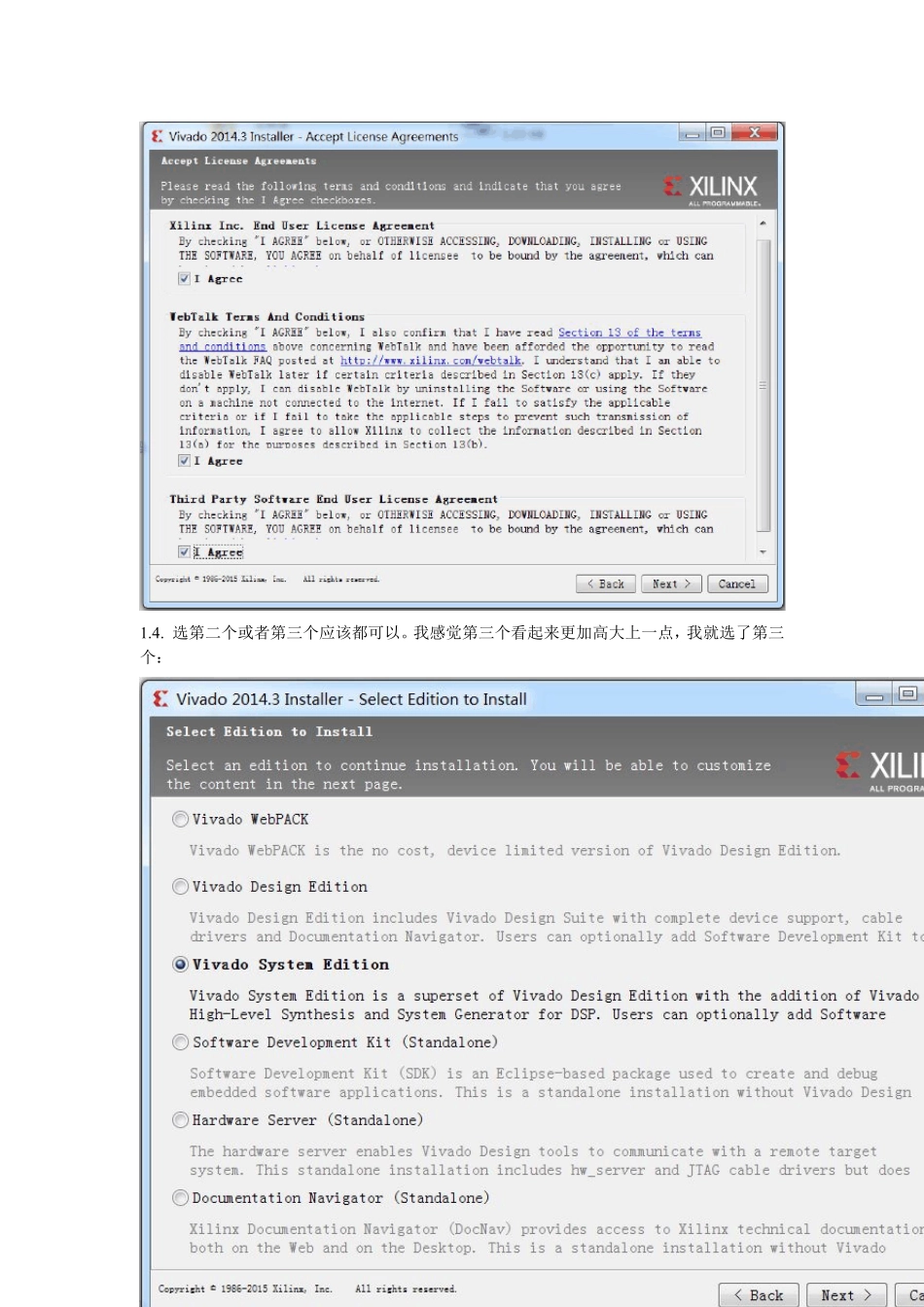

选一些根本看都不会看的I agree

选第二个或者第三个应该都可以

我感觉第三个看起来更加高大上一点,我就选了第三个:1

直接点nex t:1

选择路径,稍等片刻就能安装完成:1

安装完成后,在开始菜单找到Xilinx Design Tools\Vivado 2014

3 文件夹,打开ManageXilinx Licenses:1

打开后选择左边的 load license 选项卡:1

点击copy license,选中刚才安装目录中的 crack 文件夹中的 license

至此Windows 下的XilinxVivado Design Suite 已经全部安装完成

二、在服务器中使用Vivado 生成bit 文件:2

由于综合和布局布线需要较好的硬件资源,所以本次流程中综合和布局布线在linux环境的服务器中完成

在linux环境中运行vivado 请确保正确安装JVM,在Windows 环境下图形界面流程完全一致

在服务器上正确安装JVM 后执行以下指令:2

执行“Vivado &”打开 Vivado

注意 Vivado 会在你执行这条命令的目录下生成一些 log信息,所以最好新建一个目录再打开 Vivado:2

点击Create New Project 建立新的项目,在弹出的对话框中点Next:2

输入项目名称,然后再点击Next:2