计算机组成原理 课程设计报告 专 业 计算机科学与技术 班 级 0901 学 号 2009115010121 姓 名 汪敏 指 导 教 师 杨维均 时 间 2011

12 湖 北 师 范 学 院 计 算 机 科 学 与 技 术 学 院 两位十进制加法计数器 一、实验目的与要求 1、学习用集成触发器构成计数器的方法 2、掌握中规模集成计数器的使用及功能测试方法 二、实验题目 设计一个 0~99计数显示电路,具有加减、清零、预置数功能

三.实验器材 2 个数码管,2 个 74KS248,2 个 74LS192(1),1 个 74LS00(),一个面包板,及若干电阻和电线

四.实验原理 计数器是一个用以实现计数功能的时序部件,它不仅可用来计脉冲数,还常用作数字系统的定时、分频和执行数字运算以及其它特定的逻辑功能

计数器种类很多

按构成计数器中的各触发器是否使用一个时钟脉冲源来分,有同步计数器和异步计数器

根据计数制的不同,分为二进制计数器,十进制计数器和任意制计数器

根据计数的增减趋势,又分为加法、减法和可逆计数器

还有可预置数和可编程序功能计数器等等

目前,无论是 TTL 还是 CMOS集成电路,都有品种较齐全的中规模集成计数器

使用者只要借助于器件手册的功能表和工作波形图以及引出端的排列,就能正确地运用这些器件

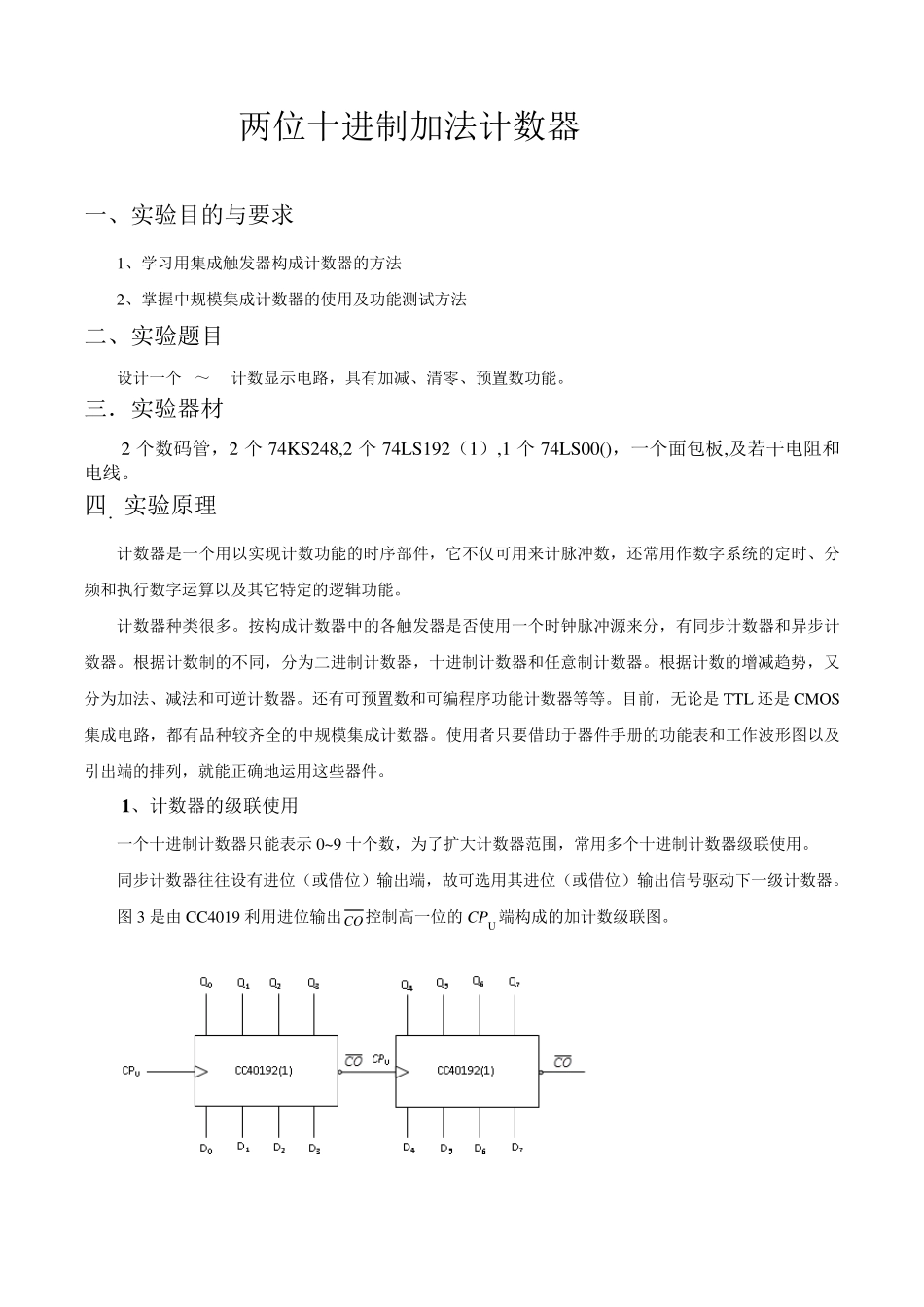

1 、计数器的级联使用 一个十进制计数器只能表示 0~9 十个数,为了扩大计数器范围,常用多个十进制计数器级联使用

同步计数器往往设有进位(或借位)输出端,故可选用其进位(或借位)输出信号驱动下一级计数器

图 3 是由 CC4019 利用进位输出CO控制高一位的 CPU 端构成的加计数级联图

图3 CC40192 级联电路 2 、实现任意进制计数 (1)用反馈清零法获得任意进制计数器 假定已有 N 进制计数器,而需要得到一个 M 进制计数器时,只要 M