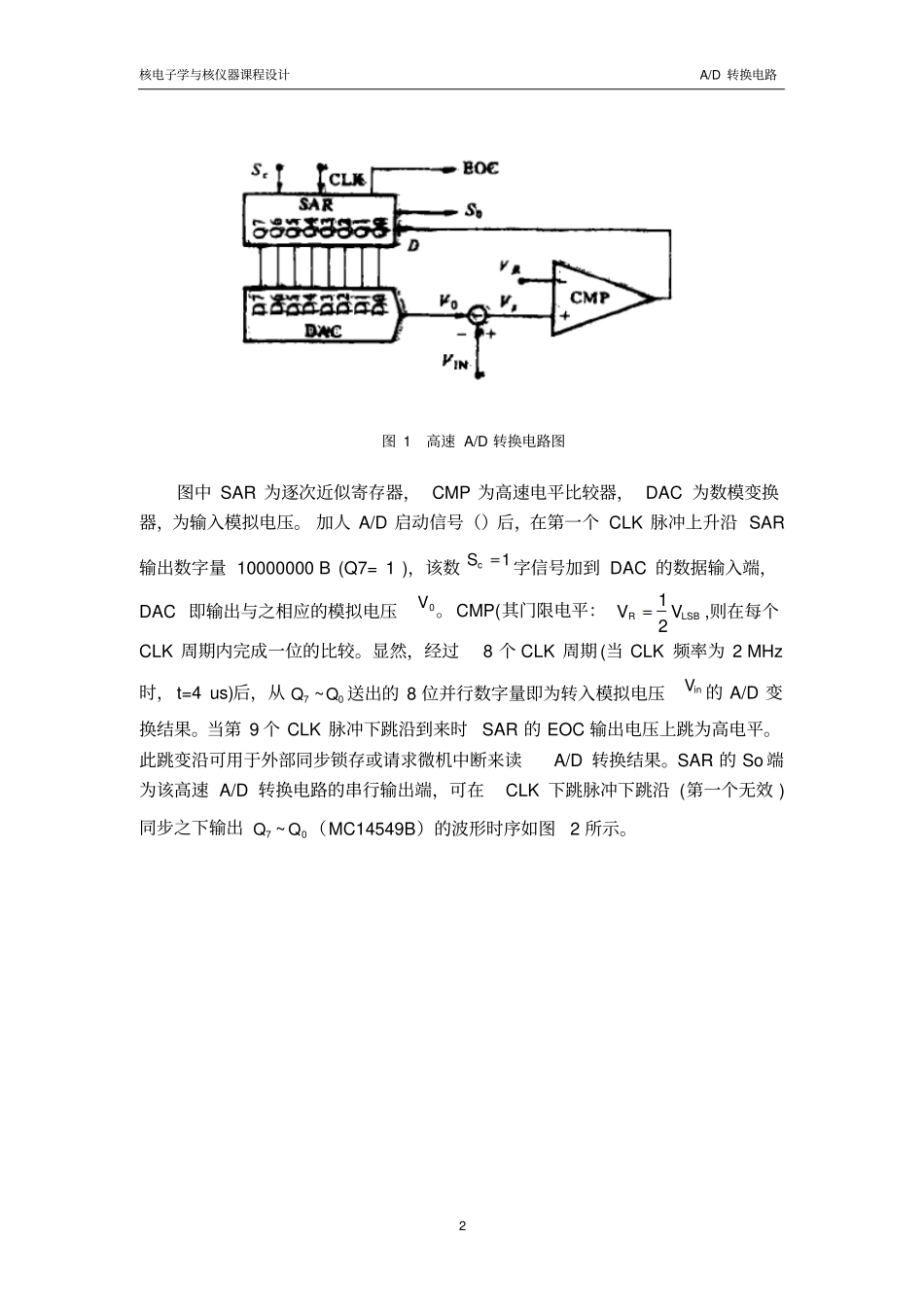

核电子学与核仪器课程设计A/D 转换电路1 8 bit/4 us高速 A/D 转换电路一、设计任务和要求(一)设计目的及任务通过 Protel2004 的电路设计,对《核电子学与核仪器》所学内容有更进一步的理解,加深印象, 使所学知识得以巩固和提高,全面掌握核电子学各模块电路的设计,实现电路设计与PCB 设计的技术环节, 提高分析问题解决问题的能力;培养学生的动手能力和遵守纪律的高尚情操还有对待工作严肃认真、一丝不苟、实事求是、不畏艰辛的优良作风,为今后从事技术工作奠定坚实的基础。(二)设计要求1、掌握 Protel2004 的使用方法;2、掌握所画电路的工作原理;3、掌握 Protel2004 电原理路图的设计;4、基本掌握使用 Protel2004 进行 PCB 设计。二、原理图选择、工作原理及分析(一)原理图的选择我们组选的题目是某种A/D 转换电路的设计,经过查书籍和资料,通过阅读东南大学报 1992 年 9 月第 22 卷增刊,我们最终选择了8 bit/4 us 高速 A/D 转换电路。对于快速过程的微机实时控制系统,时间资源通常较为紧张.为了有充分的时间去完成数据处理、状态检测及各种控制功能,一般都希望模数(A/D) 转换能在数微秒内完成。 为此,笔者采用逐次近似寄存器(SAR)MC 14549 B,廉价的高速D/A 变换器 DAC0800 及高速电平比较器LM319 等器件,研制了4 us 8 位高速A/D 转换电路。实际使用表明,当输入时钟(CLK) 频率为 2 MHz 时,该 A/D 转换电路能在 4us 内完成 8 位逐次比较变换,且工作可靠稳定,价格便宜,易于和各种微机接口。(二) 8 bit/4 us 高速 A/D 转换电路图的工作原理图 1 为该高速 A/D 转换电路的原理框图。核电子学与核仪器课程设计A/D 转换电路2 图 1 高速 A/D 转换电路图图中 SAR 为逐次近似寄存器, CMP 为高速电平比较器, DAC 为数模变换器,为输入模拟电压。 加人 A/D 启动信号()后,在第一个 CLK 脉冲上升沿 SAR输出数字量 10000000 B (Q7= 1 ),该数1cS字信号加到 DAC 的数据输入端,DAC 即输出与之相应的模拟电压0V 。 CMP(其门限电平:LSBRVV21,则在每个CLK 周期内完成一位的比较。显然,经过8 个 CLK 周期 (当 CLK 频率为 2 MHz时, t=4 us)后,从7Q ~0Q 送出的 8 位并行数字量即为转入模拟电压inV 的 A/D 变换结果。当第 9 个 CLK 脉冲下跳沿到来时SAR 的 EOC 输出电压上跳为高电平。此跳变沿可用于外部同步...