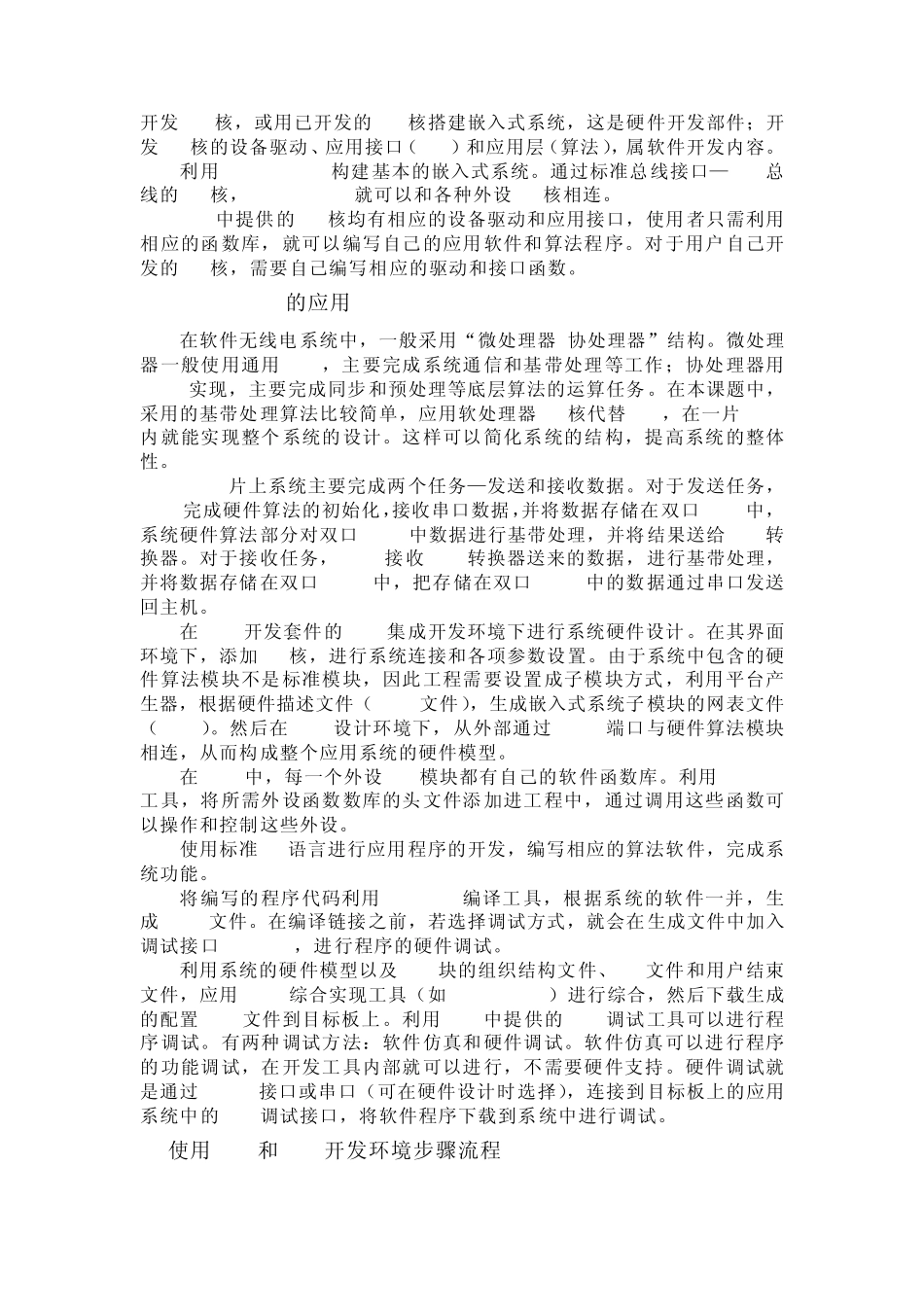

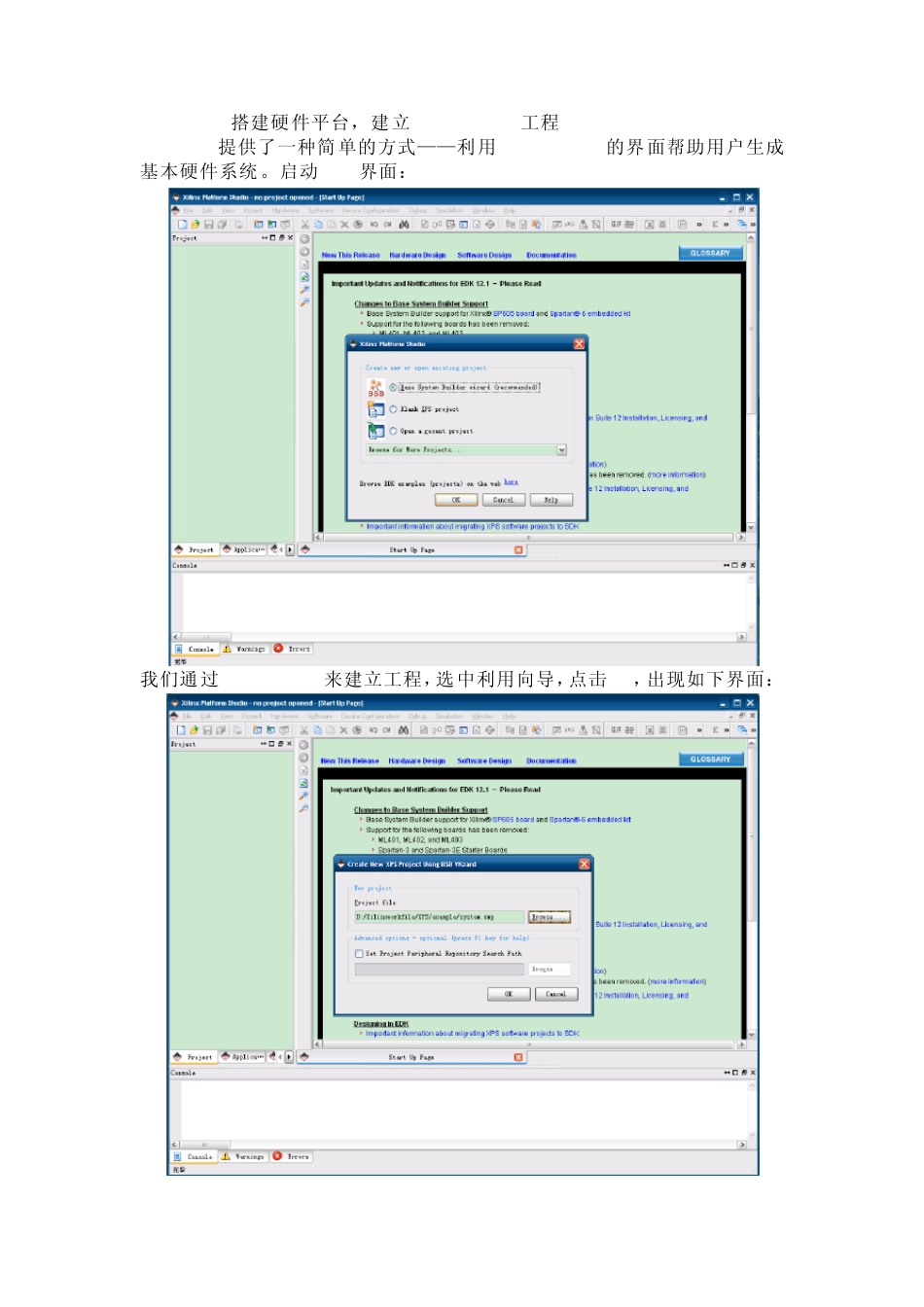

基于 Xilinx FPGA的数据通信设计流程 EDK是 Xilinx公司在可编程逻辑器件上进行嵌入式处理器系统设计的一系列软件工具,它支持 IBM PowerPC处理器硬核和 Xilinx公司的 MicroBlaze处理器软核

EDK包括如下部分: Xilinx Platform Studio(XPS)图形界面; 嵌入式系统工具集; 嵌入式处理 IP核,比如处理器和外围设备; Platform Studio SDK(软件开发工具),可用于开发嵌入式应用程序

MicroBlaze嵌入式软核是一个被 Xilinx公司优化过的可以嵌入在 FPGA中的 RISC处理器软核,具有运行速度快、占用资源少、可配置性强等优点,广泛应用于通信、军事、高端消费市场等领域

MicroBlaze的体系结构 MicroBlaze 是基于 Xilinx公司 FPGA的微处理器 IP核,和其它外设IP核一起,可以完成可编程系统芯片(SOPC)的设计

MicroBlaze 处理器采用 RISC架构和哈佛结构的 32位指令和数据总线,可以全速执行存储在片上存储器和外部存储器中的程序,并和其它外设 IP核一起,可以完成可编程系统芯片(SOPC)的设计

MicroBlaze处理器采用 RISC架构和哈佛结构的 32位指令和数据总线,可以全速执行存储在片上存储器和外部存储器中的程序,并访问其的数据

MicroBlaze内部有 32个 32位通用寄存器和 2个 32位特殊寄存器—PC指针和 MSR状态标志寄存器

为了提高性能,MicroBlaze还具有指令和数据缓存

所有的指令字长都是 32位,有 3个操作数和 2种寻址模式

指令按功能划分有逻辑运算、算术运算、分支、存储器读/写和特殊指令等

指令执行的流水线是并行流水线,它分为 3级流水:取指、译码和执行

MicroBlaze可以响应软件和硬件中