平台 软件:ModelSim-Altera 6

5e (Qu artu s II 10

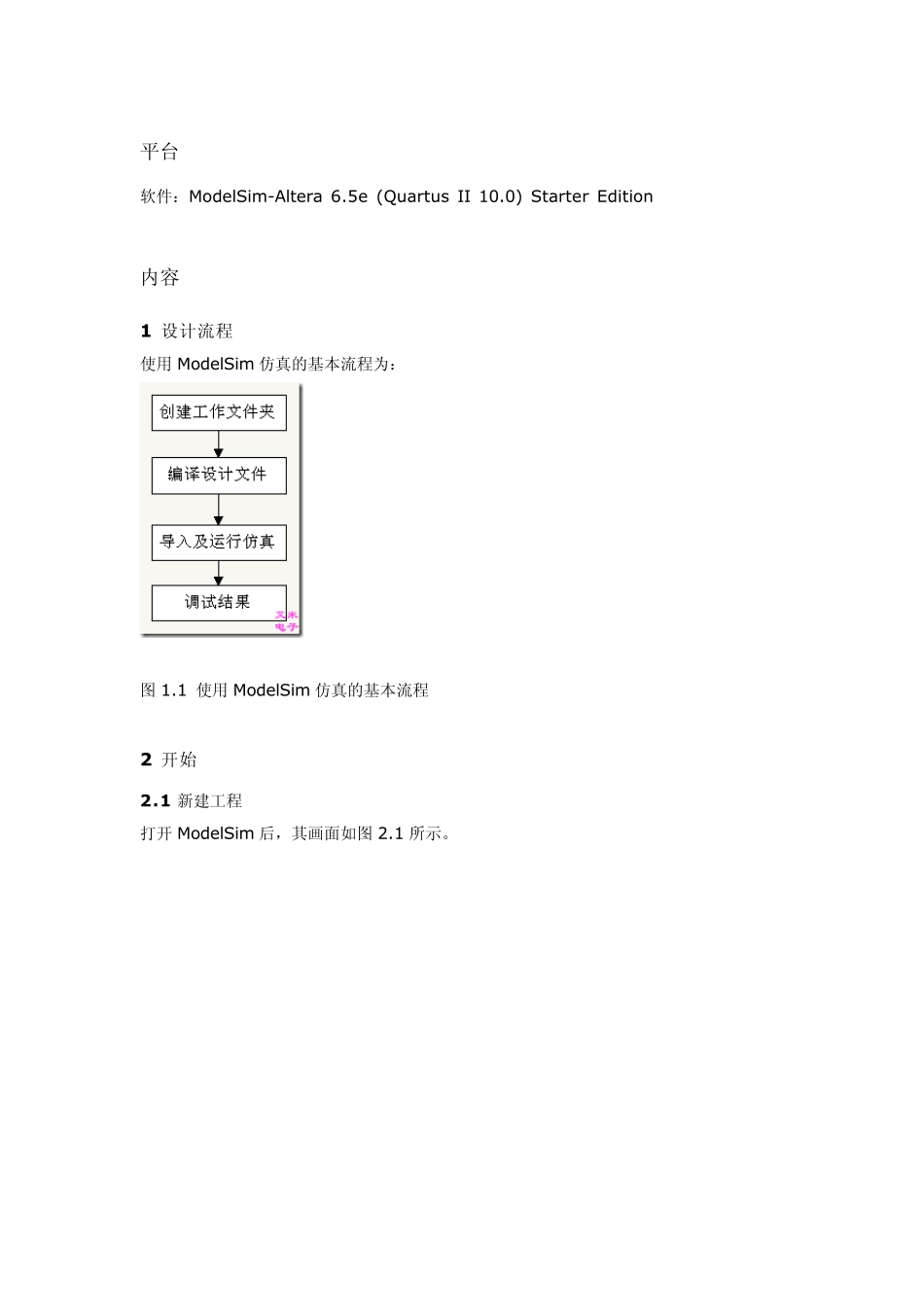

0) Starter Edition 内容 1 设计流程 使用ModelSim 仿真的基本流程为: 图1

1 使用ModelSim 仿真的基本流程 2 开始 2

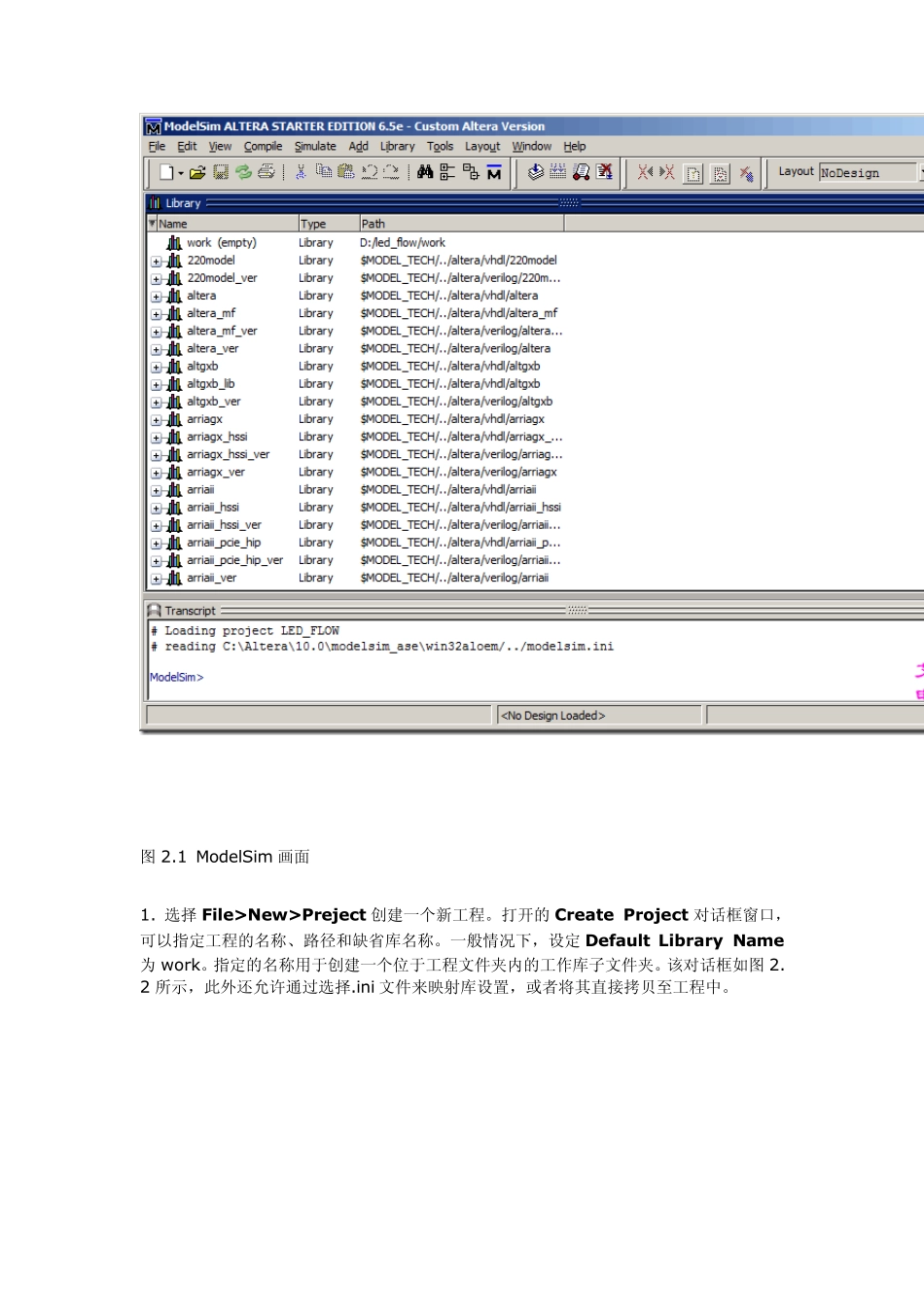

1 新建工程 打开ModelSim 后,其画面如图2

1 ModelSim 画面 1

选择File>New>Preject 创建一个新工程

打开的Create Project 对话框窗口,可以指定工程的名称、路径和缺省库名称

一般情况下,设定Default Library Name为 w ork

指定的名称用于创建一个位于工程文件夹内的工作库子文件夹

该对话框如图2

2 所示,此外还允许通过选择

ini 文件来映射库设置,或者将其直接拷贝至工程中

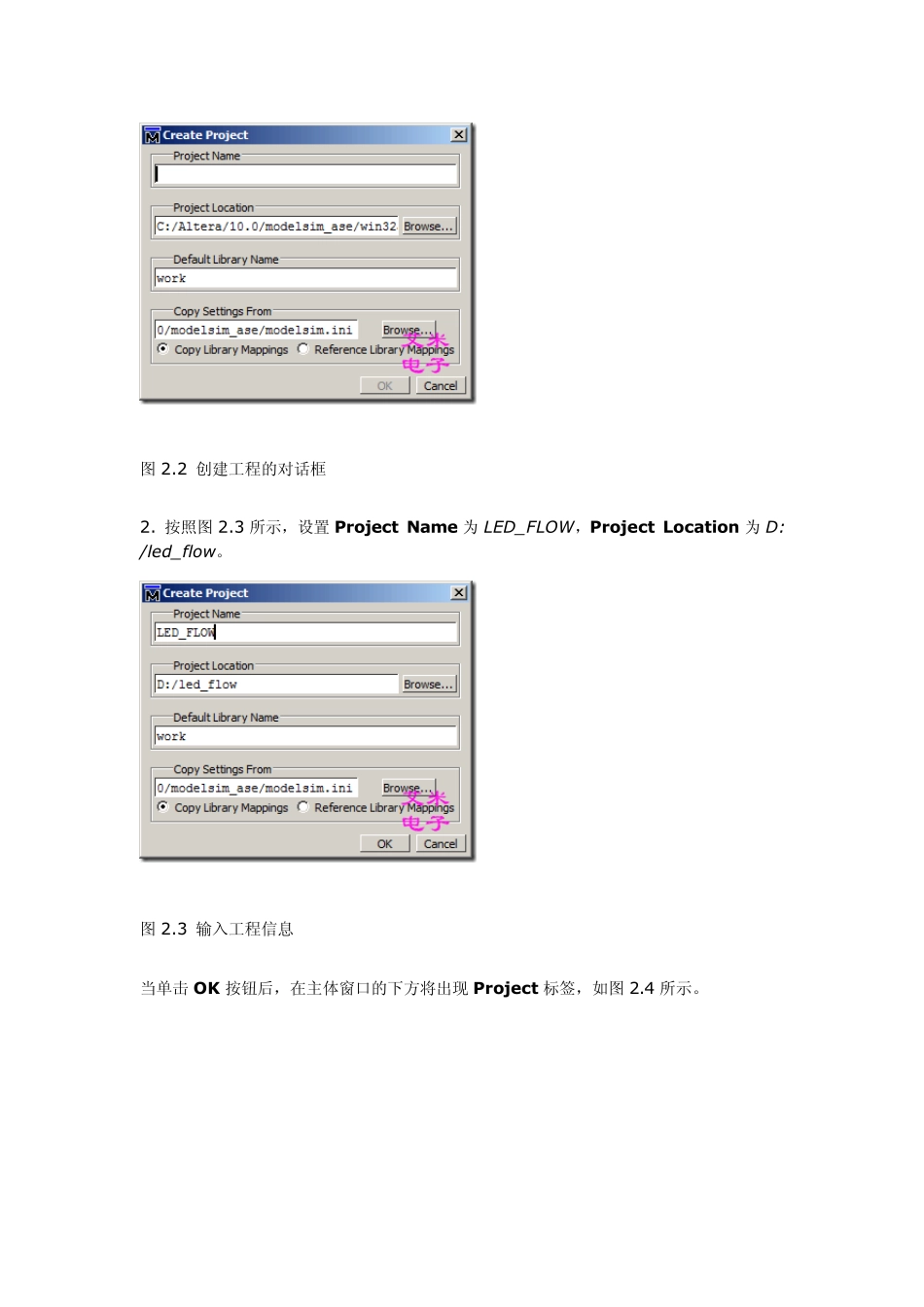

2 创建工程的对话框 2

3 所示,设置Project Name 为LED_FLOW,Project Location 为D:/led_flow

3 输入工程信息 当单击 OK 按钮后,在主体窗口的下方将出现 Project 标签,如图2

4 Project 标签 3

之后,将出现Add Items to the Project 的对话框,如图2

5 在工程中,添加新项目 2

2 在工程中,添加新项目 在Add Items to the Project 对话框中,包括以下选项: Create New File——使用源文件编辑器创建一个新的Verilog、VHDL、TCL或文本文件 Add Existing File——添加一个已存在的文件 Create Simulation——创建指定源文件和仿真选项的仿真配置 Create New Folder——创建一个新的组织文件夹 1