奇数分频器 1 引言 分频器在CPLD/FPGA 设计中使用频率非常高,尽管目前大部分设计中采用芯片厂家集成的锁相环资源,但是对于要求奇数倍分频、小数倍分频的应用场合却往往不能满足要求

硬件工程师希望有一种灵活的设计方法,根据需要,在实验室就能设计分频器并马上投入使用,更改频率时无需改动原器件或电路板,只需重新编程,在数分钟内即可完成

对于偶数分频,使用一模 N 计数器模块即可实现,即每当模 N 计数器从 0 开始计数至 N 时,输出时钟进行翻转,同时使计数器复位,使之从 0开始重新计数,以此循环即可实现

但对于奇数分频,实现 50%的占空比却是比较困难的

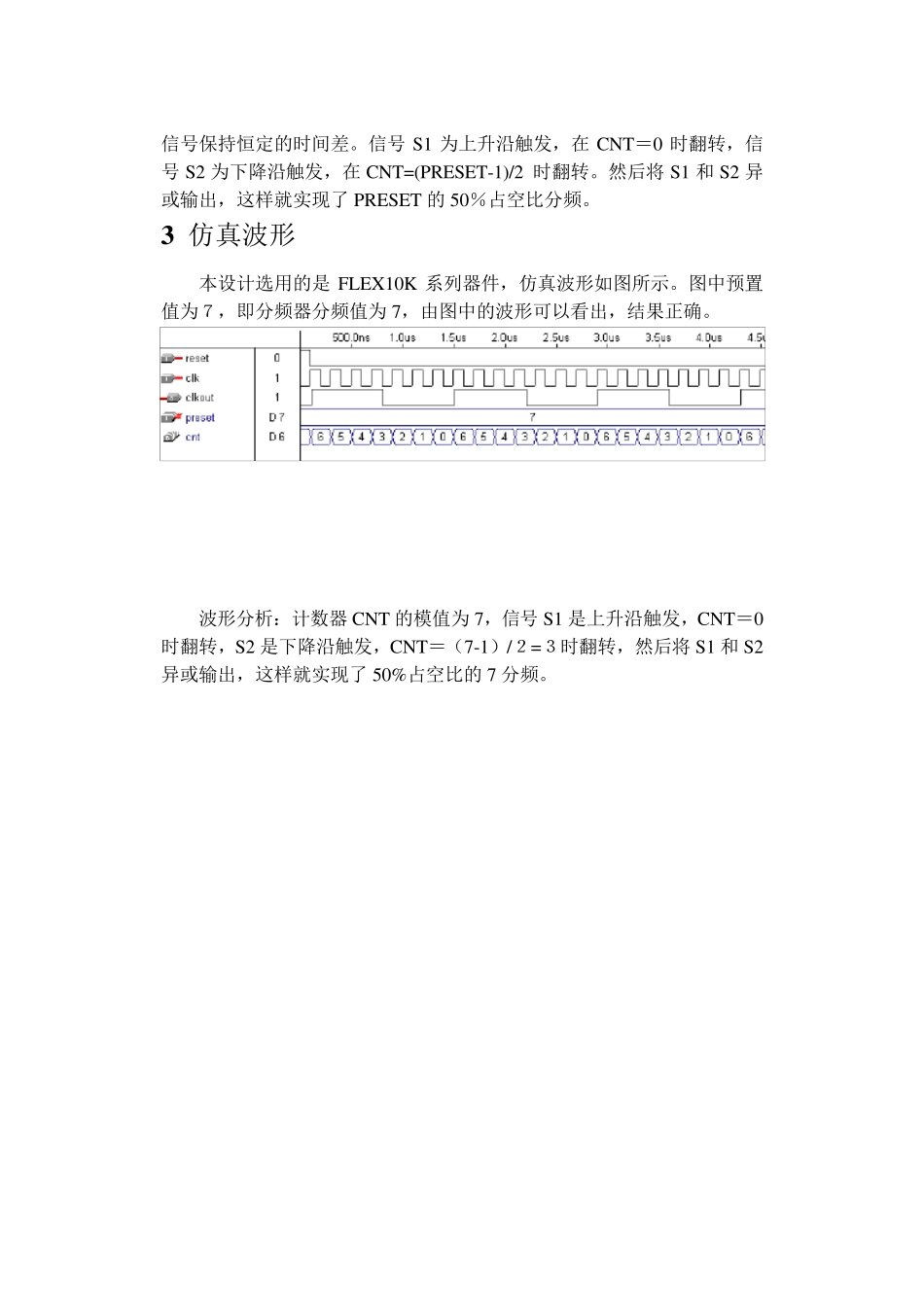

下面给出占空比 50%的奇数分频器的设计源程序和仿真结果

2 VHDL 程序 LIBRARY IEEE; USE IEEE

STD_LOGIC_1164

ALL; USE IEEE

STD_LOGIC_UNSIGNED

ALL; --添加库 ENTITY fdiv IS --设计实体 PORT( clk,reset : IN STD_LOGIC; --端口说明 preset: IN INTEGER; --preset: 分频预置数 clkou t : OUT STD_LOGIC); - -clkou t : 分频后得到的时钟 END fdiv ; ARCHITECTURE behav e OF fdiv IS --设计构造体 SIGNAL s1,s2 : STD_LOGIC; --内部信号 s1,s2 SIGNAL cnt : INTEGER RANGE 0 TO preset-1; --模为 preset 的计数信号 BEGIN P1: PROCESS(clk,reset) --计数器 BEGIN IF reset='1' THEN cnt