2 时序逻辑电路的设计方法 本次重点内容: 1、同步时序逻辑电路的设计方法

2、异步时序逻辑电路的设计方法

教学过程 5

1 同步时序逻辑电路的设计 一、同步时序逻辑电路的设计方法 设计关键:根据设计要求→确定状态转换的规律→求出各触发器的驱动方程

设计步骤:(先简单介绍,通过以下的举例后,再进行总结,特别再点出设计关键) 1.根据设计要求,设定状态,确定触发器数目和类型

画出状态转换图

2.状态化简 前提:保证满足逻辑功能要求

方法:将等价状态(多余的重复状态)合并为一个状态

3.状态分配,列出状态转换编码表 通常采用自然二进制数进行编码

N 为电路的状态数

每个触发器表示一位二进制数,因此,触发器的数目n 可按下式确定 2n≥N>2n–1 4.画状态转换卡诺图,求出状态方程、输出方程 选择触发器的类型(一般可选 JKF/F 或 DF/F,由于 JK 触发器使用比较灵活,因此,在设计中多选用JK 触发器

)将状态方程和触发器的特性方程进行比较→驱动方程

5.根据驱动方程和输出方程画逻辑图

6.检查电路有无自启动能力

如设计的电路存在无效状态时,应检查电路进入无效状态后,能否在时钟脉冲作用下自动返回有效状态工作

如能回到有效状态,则电路有自启动能力;如不能,则需修改设计,使电路具有自启动能力

二、 同步时序逻辑电路的设计举例 [例1] 试设计一个同步七进制加法计数器

解:设计步骤 (1)根据设计要求,设定状态,画状态转换图

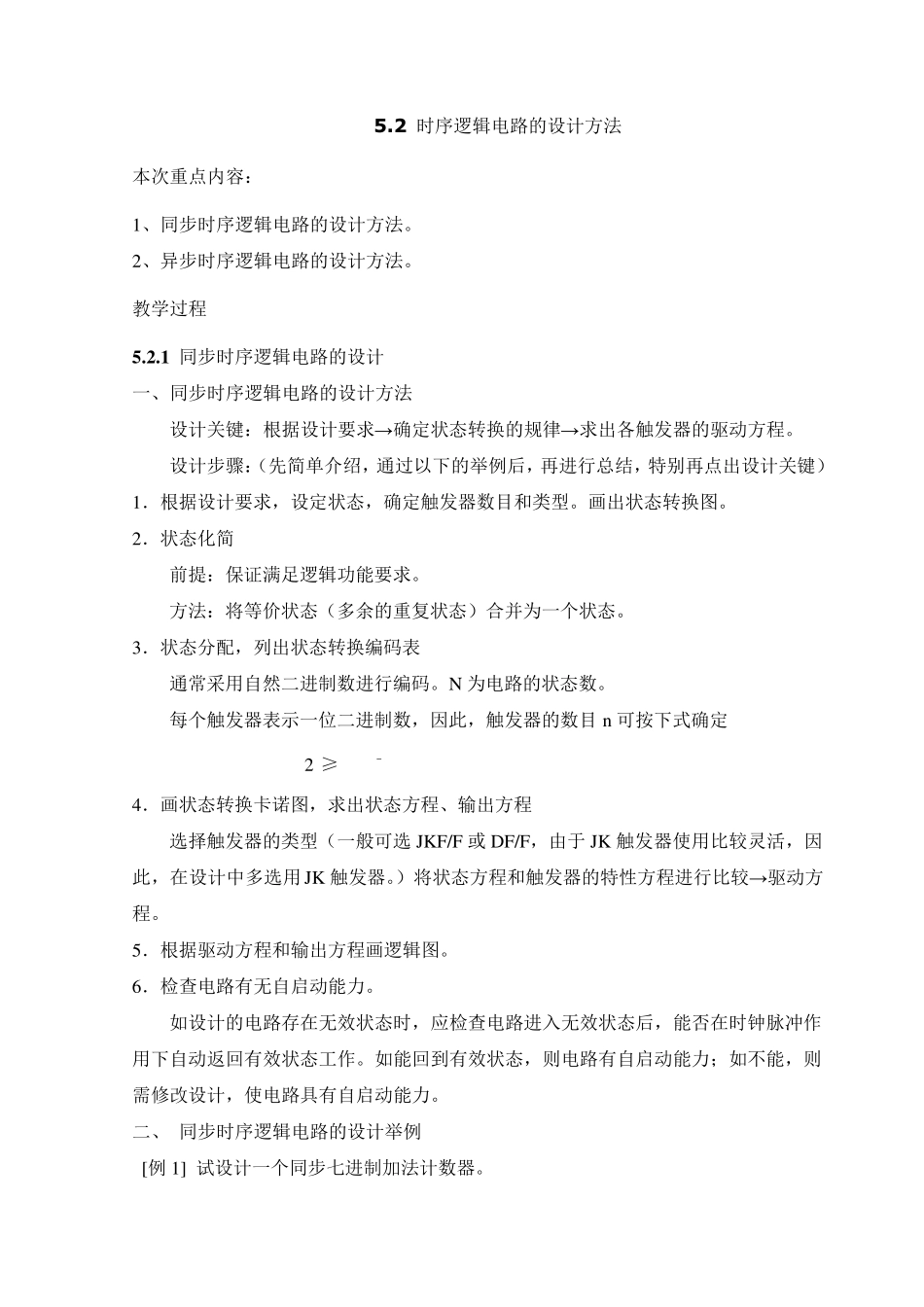

七进制→ 7 个状态→ 用S0,S1,… ,S6 表示 状态转换图如下所示: 000001010011100101110 (2)状态化简

本例中7 个状态都是有效状态

(3)状态分配,列状态转换编码表

根据式2n≥N>2n–1,→ N=7,n=3,即采用三个触发器

选用三位自然二进制加法计数编码→ 列出状态转