计数器的原理计数器是数字电路中广泛使用的逻辑部件,是时序逻辑电路中最重要的逻辑部件之一

计数器除用于对输入脉冲的个数进行计数外,还可以用于分频、定时、产生节拍脉冲等

计数器按计数脉冲的作用方式分类,有同步计数器和异步计数器;按功能分类,有加法计数器、减法计数器和既具有加法又有减法的可逆计数器;按计数进制的不同,又可分为二进制计数器、十进制计数器和任意进制计数器

一、计数器的工作原理1、二进制计数器(1)异步二进制加法计数器图 1 所示为用 JK 触发器组成的 4 位异步二进制加法计数器逻辑图

图中4 个触发器 F0~F3 均处于计数工作状态

计数脉冲从最低位触发器F0的CP 端输入,每输入一个计数脉冲,F0 的状态改变一次

低位触发器的Q 端与高位触发器的 CP 端相连

每当低位触发器的状态由1 变 0 时,即输出一负跳变脉冲时,高位触发器翻转

各触发器置0 端 RD 并联,作为清 0 端,清 0 后,使触发器初态为0000

当第一个计数脉冲输入后,脉冲后沿使F0的 Q0由 0 变 1,F1、F2、F3均保持 0 态,计数器的状态为0001;当图 1 4 位异步二进制加法计数器第二个计数脉冲输入后,Q0由 1 变为 0,但 Q0的这个负跳变加至F1 的 CP 端,使 Q1由 0变为 1,而此时 F3、F2仍保持 0 状态,计数器的状态为0010

依此类推,对于F0来说,每来一个计数脉冲后沿, Q0 的状态就改变,而对于F1、F2、F3来说,则要看前一位输出端Q是否从 1 跳到 0,即后沿到来时,其输出端的状态才改变,否则Q1、Q2、Q3 端的状态同前一个状态一样

这样在第15 个计数脉冲输入后,计数器的状态为1111,第 16 个计数脉冲输入,计数器恢复为0000

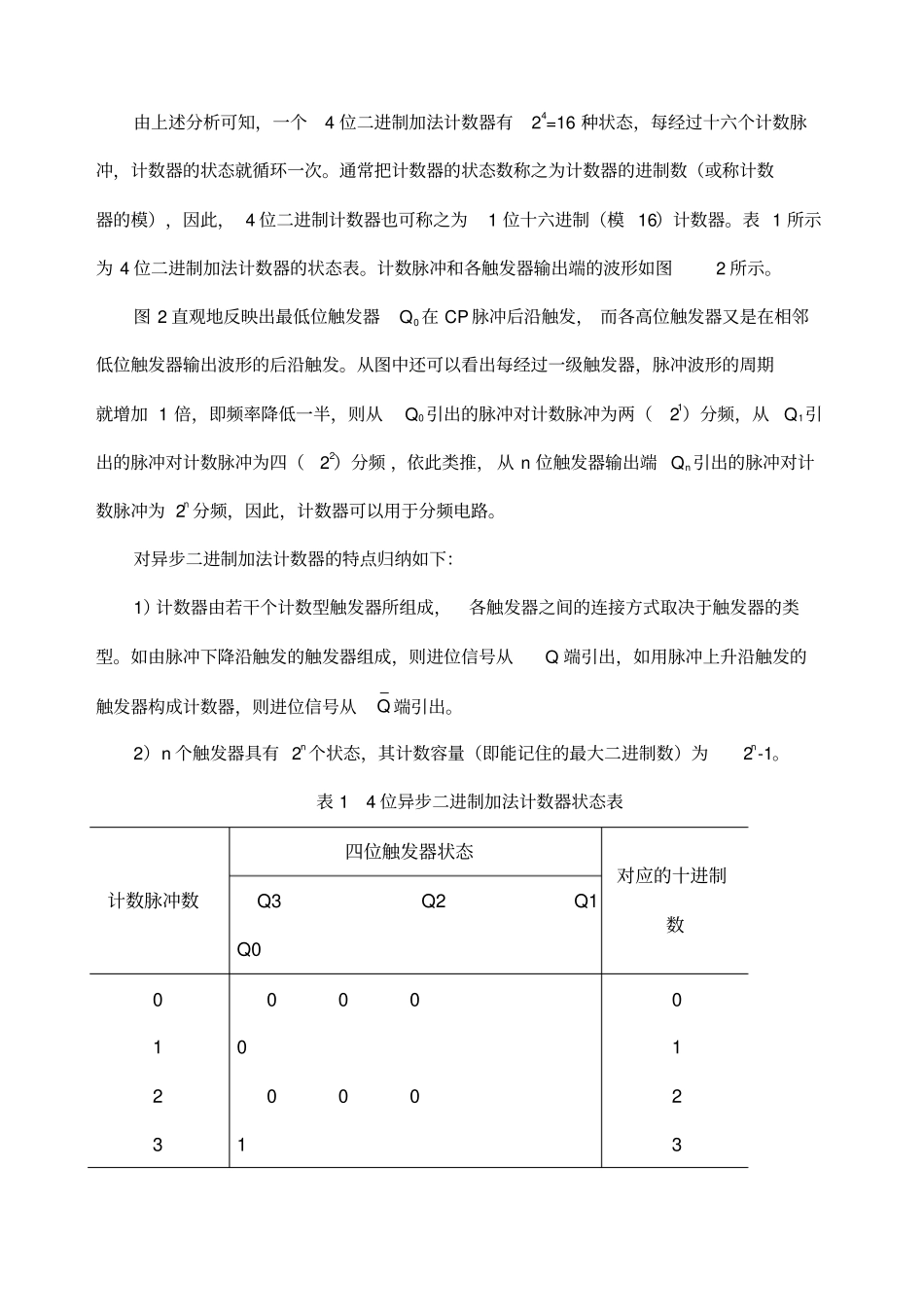

由上述分析可知,一个4 位二进制加法计数器有24=16 种状态,每经过十六个计数脉冲,计数器的状态就循环一次