1 实验一Quartus II 使用与基本逻辑电路的设计[ 实验目的 ] 1、熟悉 Quartus II 的文本输入方式, 掌握其编辑、编译综合、仿真的操作方法;2、学习 Quartus II 环境下的编程下载及硬件测试方法;3、学习应用QuartusII 完成基本时序电路设计;4、应用 QuartusII 完成基本组合电路的设计

* [ 实验仪器 ]PC 机 、EDA 实验箱一台Quartus II 6

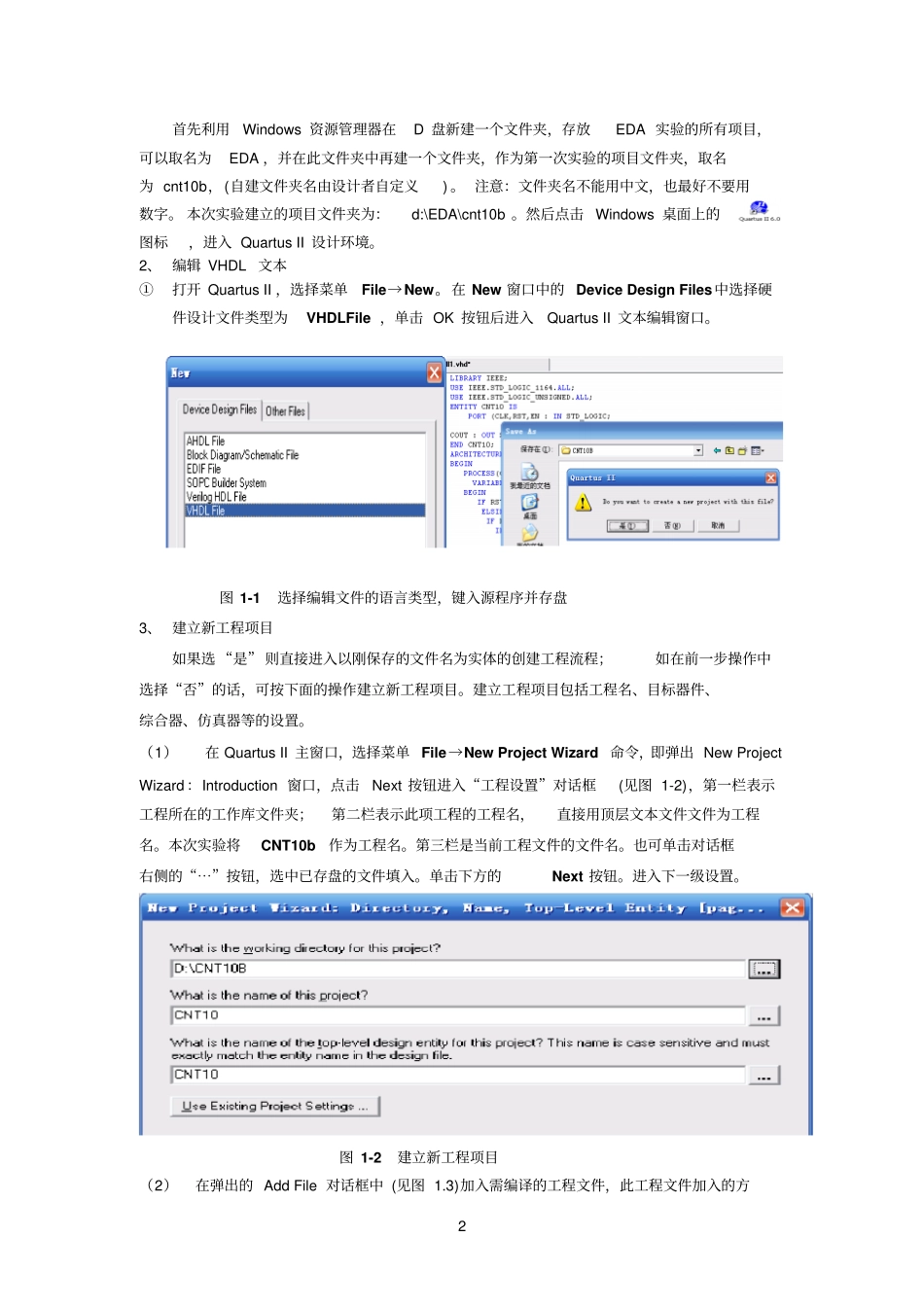

0 软件[ 实验内容 ] (1) 实验内容 1:在 QuartusⅡ上输入该设计的文本,并进行编辑、编译、综合、适配、仿真

说明设计中各语句的作用,详细描述设计的功能特点,给出其所有信号的时序仿真波形

(2) 实验内容2:引脚锁定以及硬件下载测试

引脚锁定后进行编译、下载和硬件测试实验

将实验过程和实验结果写进实验报告

* (3) 实验内容 3:使用 SignalTap II 对此计数器进行实时测试,流程与要求参考4

* (4) 实验内容 4:从设计中去除SignalTap II ,要求全程编译后生成用于配置器件EPCS1编程的压缩POF 文件,并使用ByteBlasterII ,通过 AS 模式对实验板上的EPCS1 进行编程,最后进行验证

*(5) 实验内容 5:为此项设计加入一个可用于SignalTap II 采样的独立的时钟输入端(采用时钟选择clock0=12MHz ,计数器时钟CLK 分别选择256Hz、16384Hz 、6MHz ),并进行实时测试

[ 实验原理 ] 数字逻辑电路中, 根据逻辑功能的不同特点,可以把数字逻辑电路分成组合逻辑电路和时序逻辑电路两大类用

在组合逻辑电路中,任意时刻的输出仅仅取决于该时刻的输入,与电路的原来状态无关; 在时序逻辑电路中, 任一时刻的输出信号不仅取决于当时的输入信号,而且还取决于电路原来的状态,也就是与电路