实验五7 段数码管显示译码器设计岭南师范学院(信息工程学院)一、实验目的:1

学会使用锁相环和分频器做分频处理并使用分频后的信号2

学习和掌握数码管的电路原理图及如何使用数码管显示相应的字符3

学习 7 段数码显示译码器设计、多层次设计方法、和总线数据输入方式的功能实现

二、实验原理:7 段数码是纯组合电路, 通常的小规模专用IC ,如 74 或 4000 系列的器件只能作十进制 BCD 码译码,然而数字系统中的数据处理和运算都是2 进制的,所以输出表达都是16 进制的,为了满足16 进制数的译码显示,最方便的方法就是利用 VHDL 译码程序在 FPGA 或 CPLD 中实现

本项实验很容易实现这一目的

作为7 段BCD 码译码器的设计,输出信号LED7S 的 7位分别接如图 7-1 数码管的 7 个段,高位在左,低位在右

三、实验仪器及设备1

FPGA(Max 10 )开发板 3

Quartus软件四、实验内容在开发板上的七段数码管实现显示数字并且自动增加五、实验步骤:1

打开 Quartus15

1建立一个工程文件2

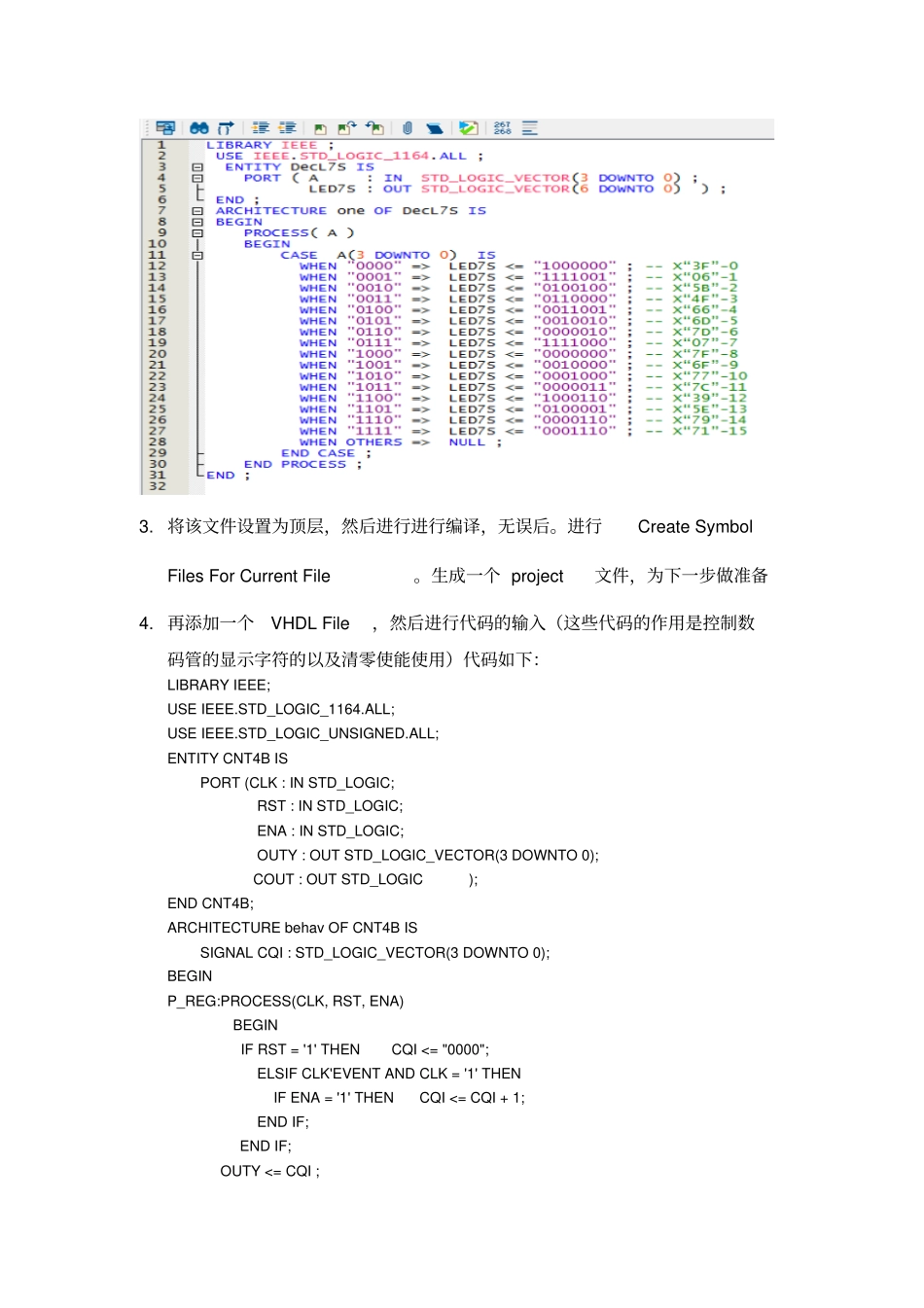

添加一个VHDL File,然后进行代码的输入(这些代码的作用是实现数码管的显示字符的)代码如下:共阴数码管及其电路LIBRARY IEEE ; USE IEEE

STD_LOGIC_1164

ALL ; ENTITY DecL7S IS PORT ( A : IN STD_LOGIC_VECTOR(3 DOWNTO 0) ; LED7S : OUT STD_LOGIC_VECTOR(6 DOWNTO 0) ) ; END ; ARCHITECTURE one OF DecL7S IS BEGIN PROCESS( A ) BEGIN CASE A(3 DOWNTO 0) IS WHEN "0000" => LED7S LED7S