百度文库1 实验五半加器、全加器及选择器、分配器一、实验目的1

掌握半加器、全加器及数据选择器、分配器工作原理2

掌握数据选择器、分配器扩展方法

熟悉常用半加器、全加器及数据选择器、分配器、的管脚排列和逻辑功能

学会分析逻辑电路的逻辑方法

二、实验器材1

数字实验箱1 台2

集成电路: 74LS00、74LS86 、74LS183、74LS151 、74LS138、各 1 片三、预习要求1.复习半加器、全加器,数据选择器、数据分配器的工作原理和特点

2.了解本实验中所用集成电路的逻辑功能和使用方法

3.准备好实验记录图表

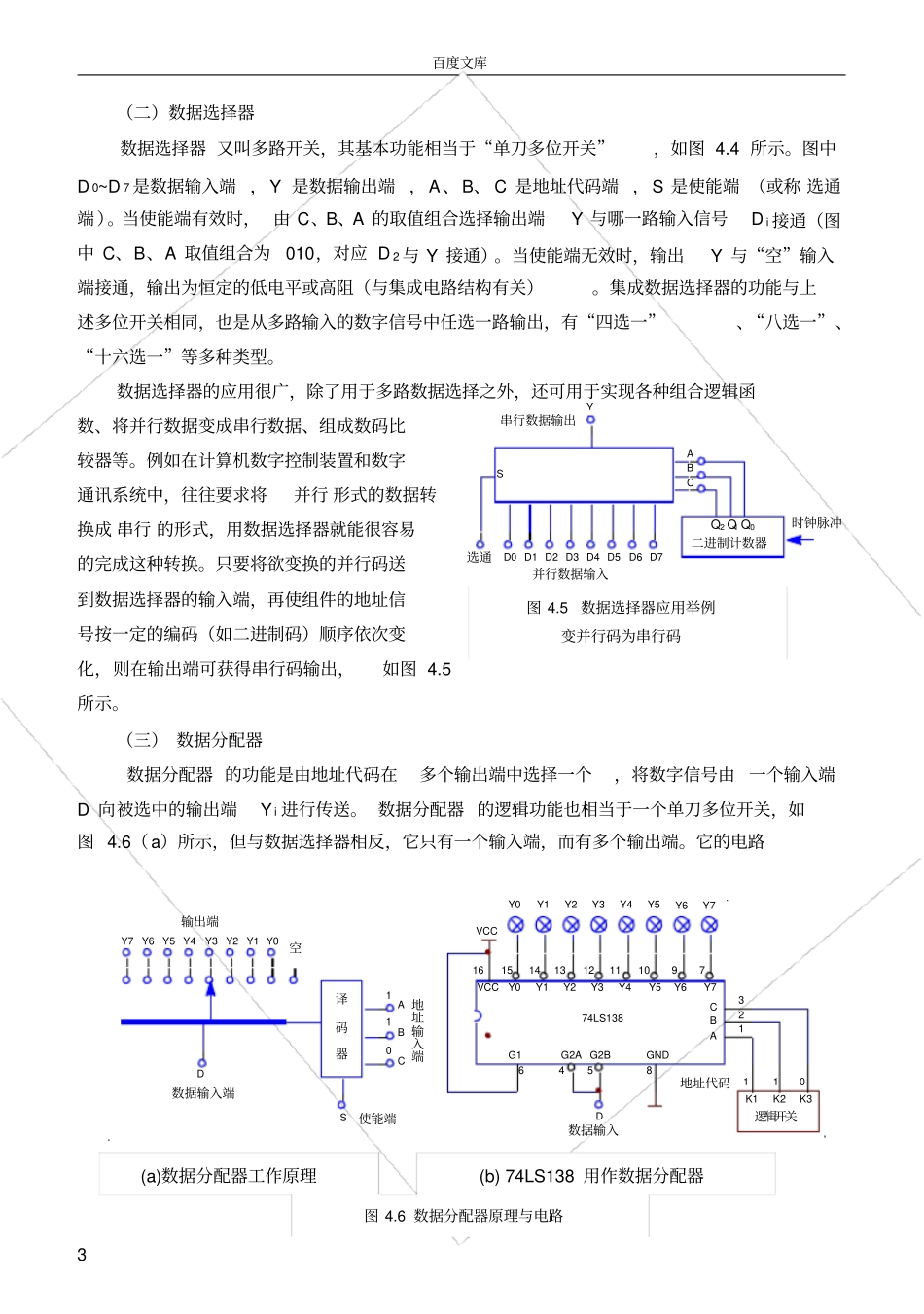

四、实验原理和电路(一)加法器加法器电路分为半加器和全加器两种

半加器在运算时不考虑前位的进位;全加器则考虑前位的进位

因此, 全加器在电路的实现上也较复杂些

1.半加器半加器的真值表见表4

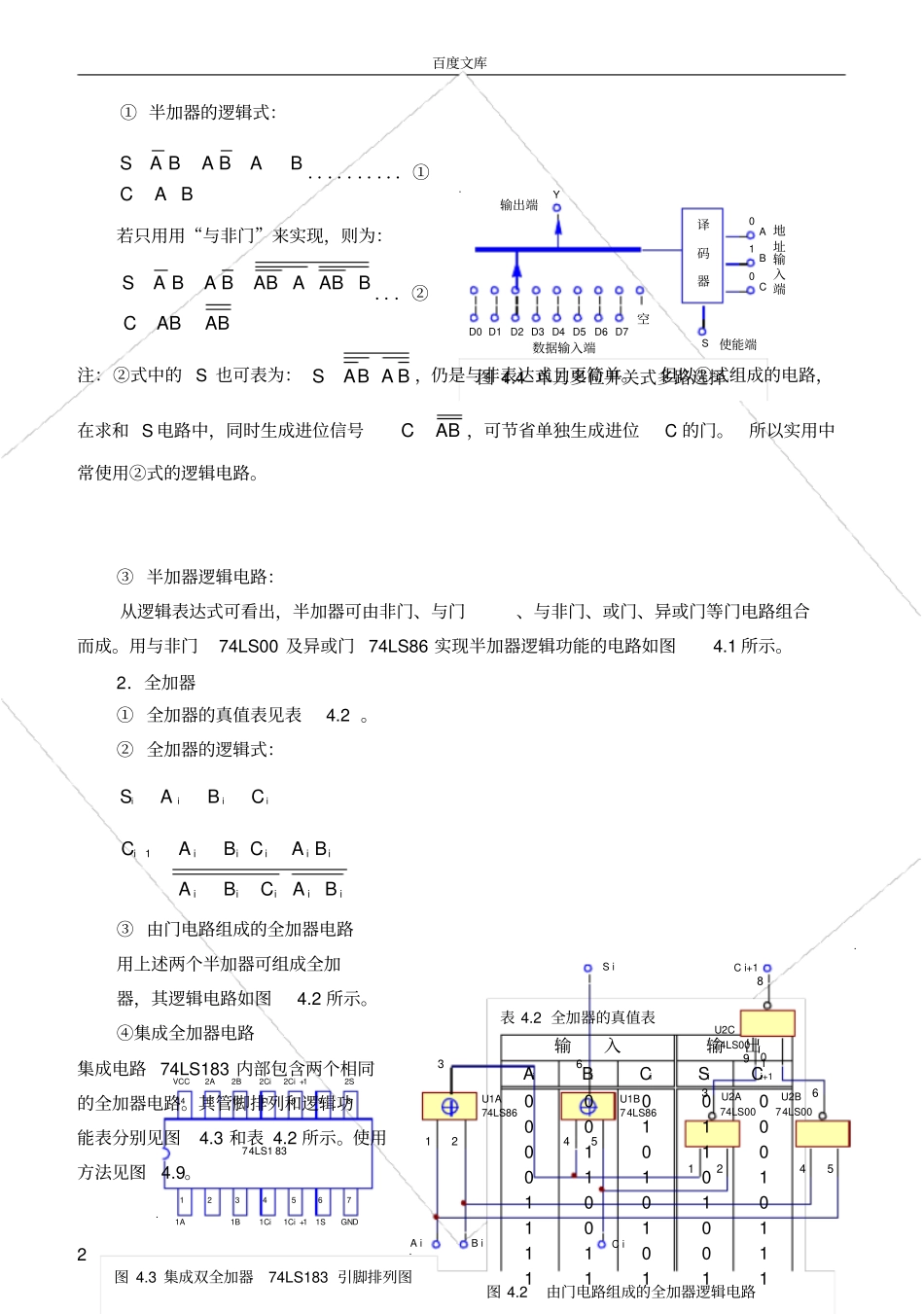

1 半加器真值表ABS C0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 1 图 4

1 半加器逻辑电路123U1A74LS86123U2A74LS00456U2B74LS00ABSC'

(b)用异或门和与非门组成123U1A74LS00456U1B74LS009108U1C74LS00121311U1D74LS00123U2A74LS00ABSC

( a)用与非门组成百度文库2 ① 半加器的逻辑式:BACBABABAS..........①若只用用“与非门”来实现,则为:ABABCBABAABBABAS...②注:②式中的 S 也可表为:BABAS,仍是与非表达式且更简单

但以②式组成的电路,在求和 S 电路中,同时生成进位信号ABC,可节省单独生成进位C 的门

所以实用中常使用②式的逻辑电路

③ 半加器逻辑电路:从逻辑表达式可看出,半加器可由非门、与门、与非门、或门、异或门等门电路组合而成

用与非门74LS