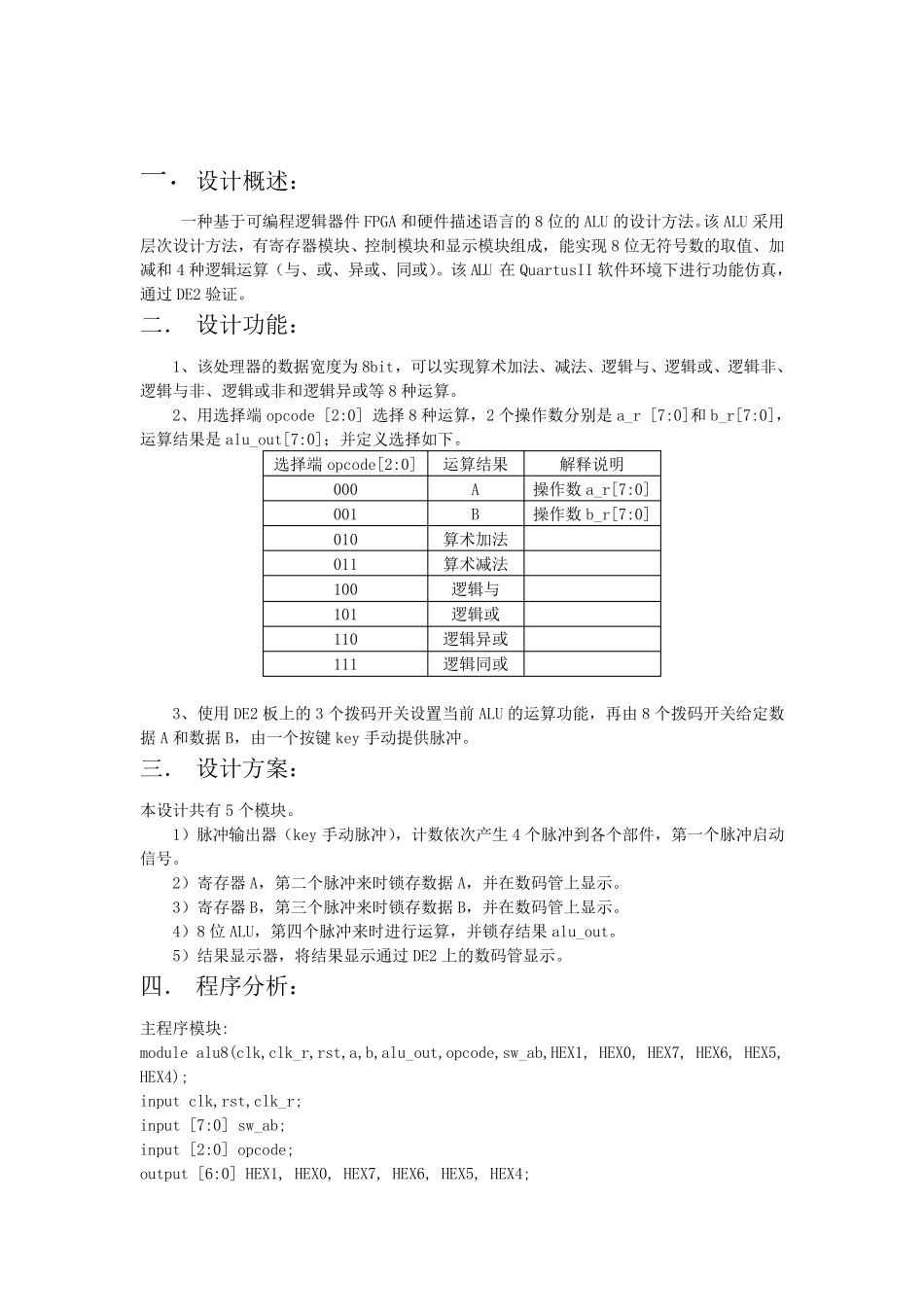

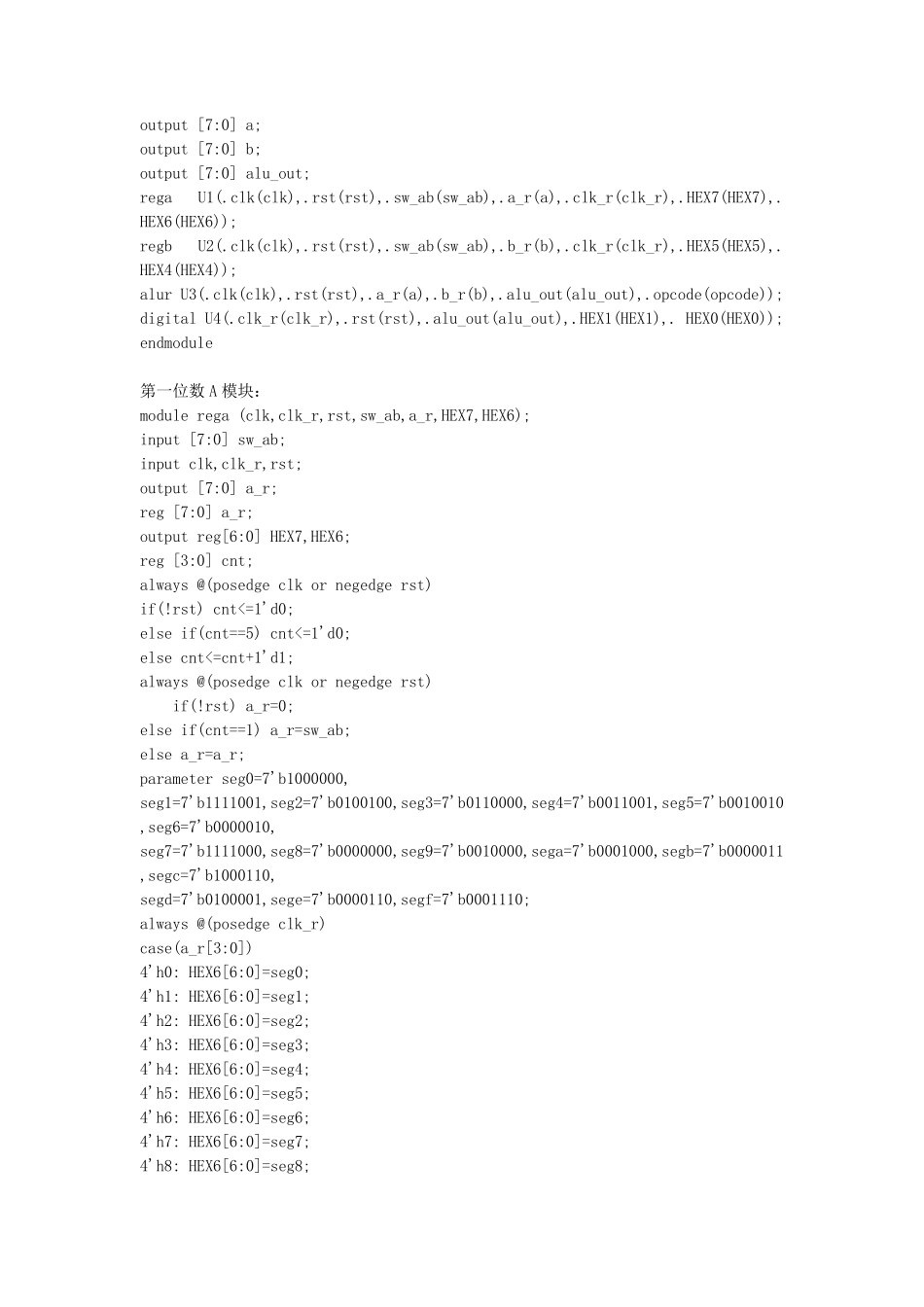

大连理工大学城市学院 FPGA 实验报告 实验内容:8 位 ALU 系别班级:电子 1004 班 学号: 姓名: 日期:2013.4.14 一.设计概述: 一种基于可编程逻辑器件FPGA 和硬件描述语言的8 位的ALU 的设计方法。该ALU 采用层次设计方法,有寄存器模块、控制模块和显示模块组成,能实现 8 位无符号数的取值、加减和4 种逻辑运算(与、或、异或、同或)。该ALU 在 QuartusII 软件环境下进行功能仿真,通过 DE2 验证。 二. 设计功能: 1、该处理器的数据宽度为 8bit,可以实现算术加法、减法、逻辑与、逻辑或、逻辑非、逻辑与非、逻辑或非和逻辑异或等 8 种运算。 2、用选择端 opcode [2:0] 选择 8 种运算,2 个操作数分别是 a_r [7:0]和b_r[7:0],运算结果是 alu_out[7:0];并定义选择如下。 选择端 opcode[2:0] 运算结果 解释说明 000 A 操作数 a_r[7:0] 001 B 操作数 b_r[7:0] 010 算术加法 011 算术减法 100 逻辑与 101 逻辑或 110 逻辑异或 111 逻辑同或 3、使用DE2 板上的3 个拨码开关设置当前 ALU 的运算功能,再由 8 个拨码开关给定数据 A 和数据 B,由一个按键 key 手动提供脉冲。 三. 设计方案: 本设计共有5 个模块。 1)脉冲输出器(key 手动脉冲),计数依次产生 4 个脉冲到各个部件,第一个脉冲启动信号。 2)寄存器A,第二个脉冲来时锁存数据 A,并在数码管上显示。 3)寄存器B,第三个脉冲来时锁存数据 B,并在数码管上显示。 4)8 位ALU,第四个脉冲来时进行运算,并锁存结果 alu_out。 5)结果显示器,将结果显示通过 DE2 上的数码管显示。 四. 程序分析: 主程序模块: module alu8(clk,clk_r,rst,a,b,alu_out,opcode,sw_ab,HEX1, HEX0, HEX7, HEX6, HEX5, HEX4); input clk,rst,clk_r; input [7:0] sw_ab; input [2:0] opcode; output [6:0] HEX1, HEX0, HEX7, HEX6, HEX5, HEX4; output [7:0] a; output [7:0] b; output [7:0] alu_out; rega U1(.clk(clk),.rst(rst),.sw_ab(sw_ab),.a_r(a),.clk_r(clk_r),.HEX7(HEX7),. HEX6(HEX6)); regb U2(.clk(clk),.rst(rst),.sw_ab(sw_ab),.b_r(b),.clk_r(clk_r),.HEX5(HEX5),. HEX4(HEX4)); alur U3(.clk(clk),.rst(rst),.a_r(a),.b_r(b),.alu_out(alu_out),.opcode(opcode)); digital U4(.clk_r(clk_r),.rst(rst),.alu_out(alu_out),.HEX1(HEX...