2×8 低噪声InGaAs/ InP APD 读出电路设计 0 引言 广告插播信息 维库最新热卖芯片: 74LS374 M54585P ATMEGA168-20AU HCPL-4701 CD4015BF3A MC68HC908JL3ECDW CXA2045Q HIP2100IBT IRFP150N MBR3045CT 在红外通信的 1 310~1 550 nm波段,高灵敏度探测材料主要有 Ge—APD和 InGaAs/InP APD,两者相比较,InGaAs/InP APD具有更高的量子效率和更低的暗电流噪声

47As/InP APD采用在n+-InP衬底上依次匹配外延 InP缓冲层、InGaAs吸收层、InGaAsP能隙渐变层、InP电荷层与 InP顶层的结构

APD探测器的最大缺点是暗电流相对于信号增益较大,所以设计 APD读出电路的关键是放大输出弱电流信号,限制噪声信号,提高信噪比

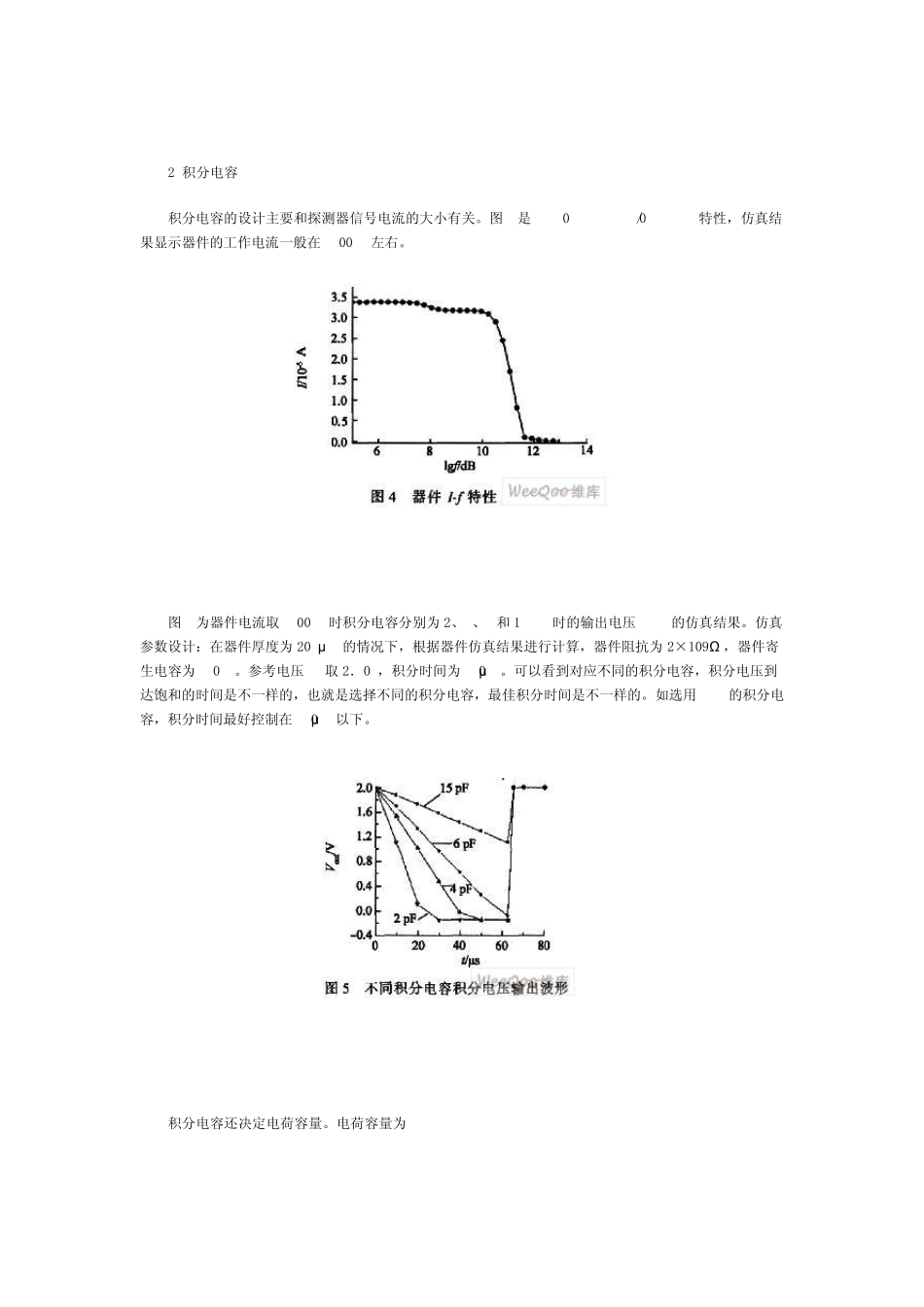

选择 CTIA作为读出单元,CTIA是采用运算放大器作为积分器的运放积分模式,比较其他的读出电路,优点是噪声低、线性好、动态范围大

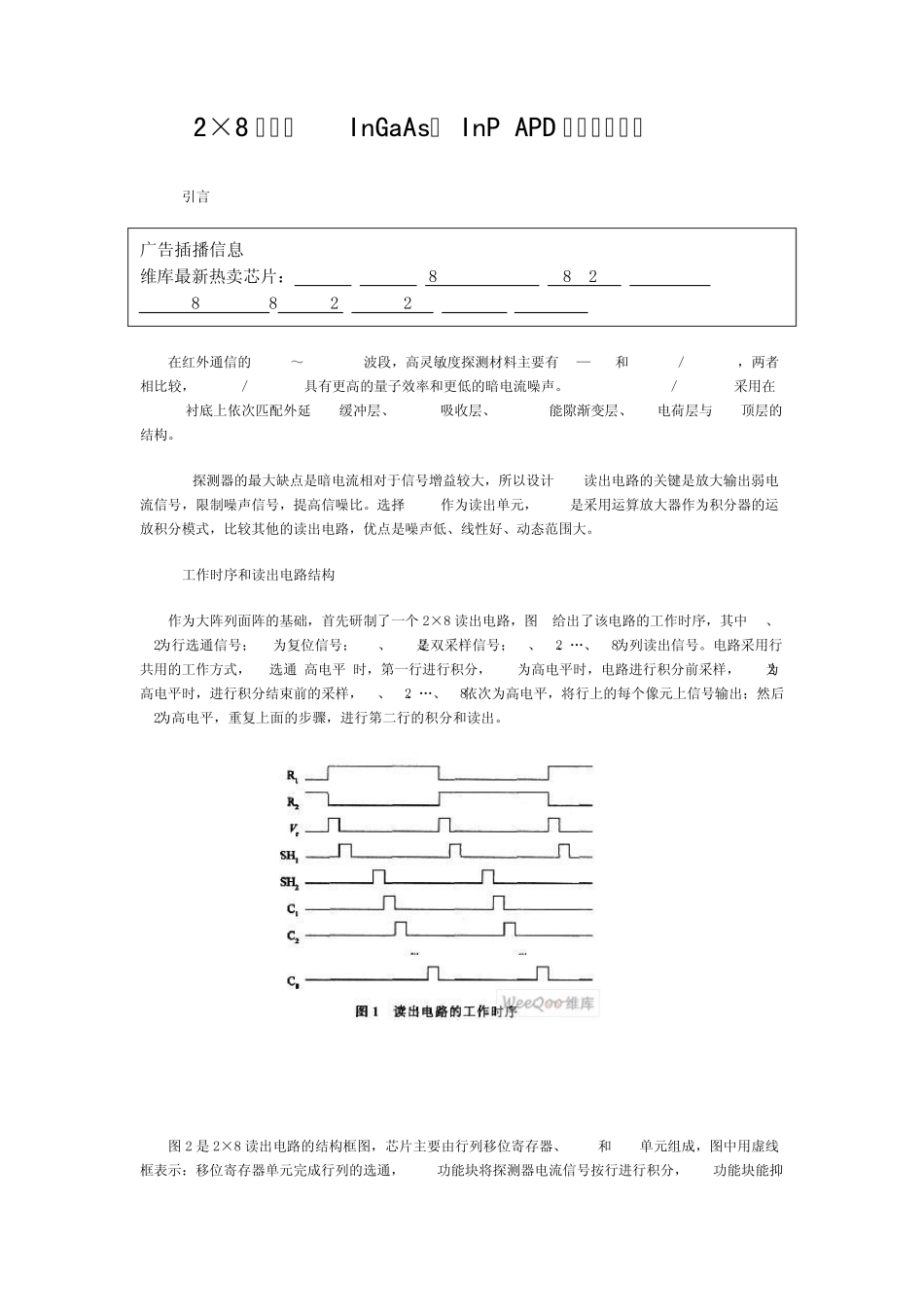

1 工作时序和读出电路结构 作为大阵列面阵的基础,首先研制了一个 2×8 读出电路,图 1给出了该电路的工作时序,其中 Rl、R2为行选通信号;Vr为复位信号;SHl、SH2是双采样信号;C1、C2、…、C8为列读出信号

电路采用行共用的工作方式,R1选通(高电平)时,第一行进行积分,SH1为高电平时,电路进行积分前采样,SH2为高电平时,进行积分结束前的采样,C1、C2、…、C8依次为高电平,将行上的每个像元上信号输出;然后R2为高电平,重复上面的步骤,进行第二行的积分和读出

图 2 是 2×8 读出电路的结构框图,芯片主要由行列移位寄存器、CTIA和 CDS单元组成,图中用虚线框表示:移位寄存器单元完成行列的选通,CTIA功能块将