本节将使用综合工具(DesignCompiler)对一个8位全加器逻辑综合,并产生一个门级网表;利用该网表使用自动布局布线工具(SiliconEnsemble)生成一个全加器的版图

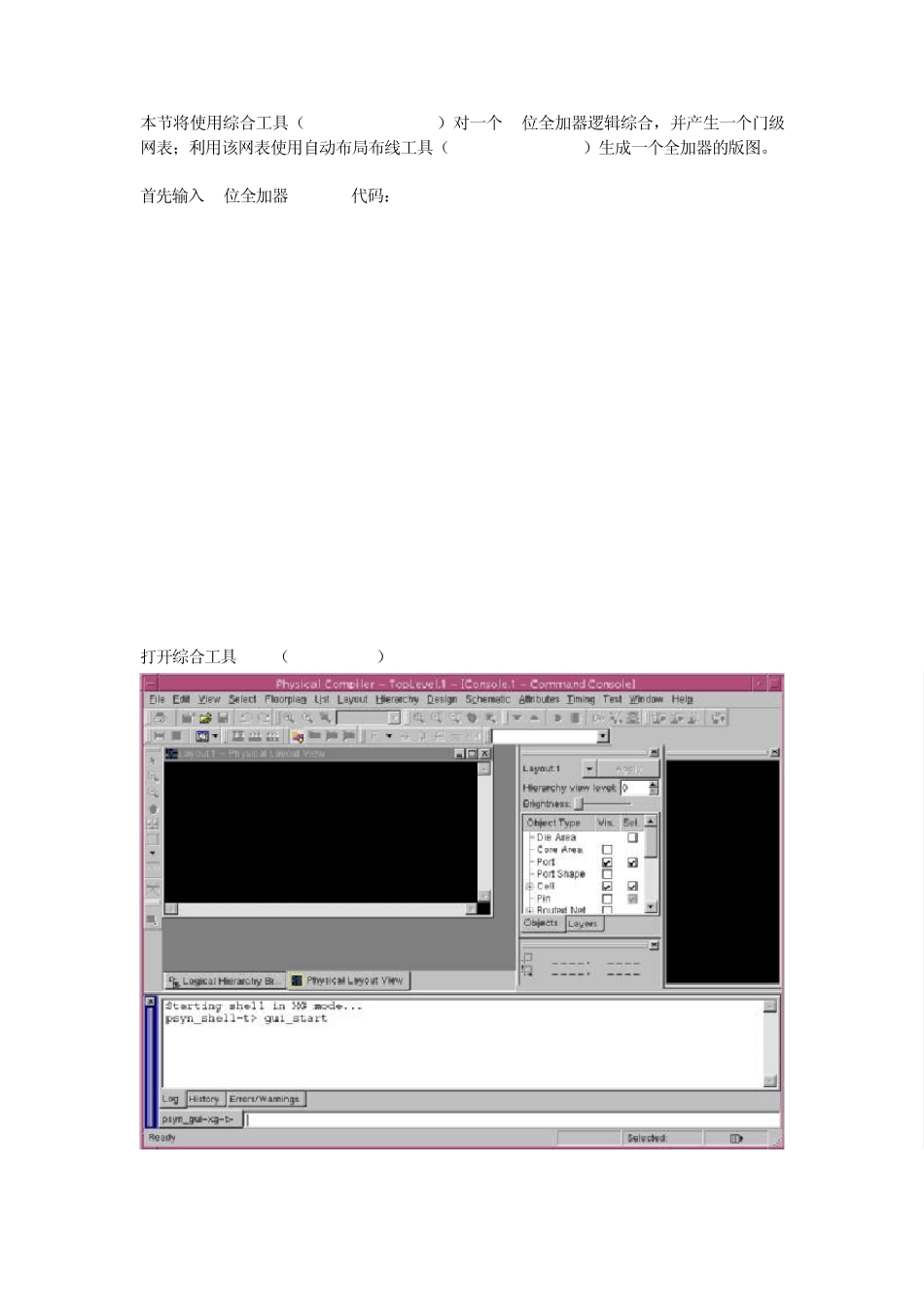

首先输入 8位全加器verilog代码:moduleadder8(Cout,S,A,Cin);outputCout;output[7:0]S;input[7:0]A;input[7:0]B;inputCin;reg[8:0]SUM;reg[7:0]S;regCout;wire[7:0]A,B;always@(AorBorCin)beginSUM[8:0]=A+B+Cin;S=SUM[7:0];Cout=SUM[8];endendmodule打开综合工具DC(psyn_gui&)File->Read

读入代码File->Setup

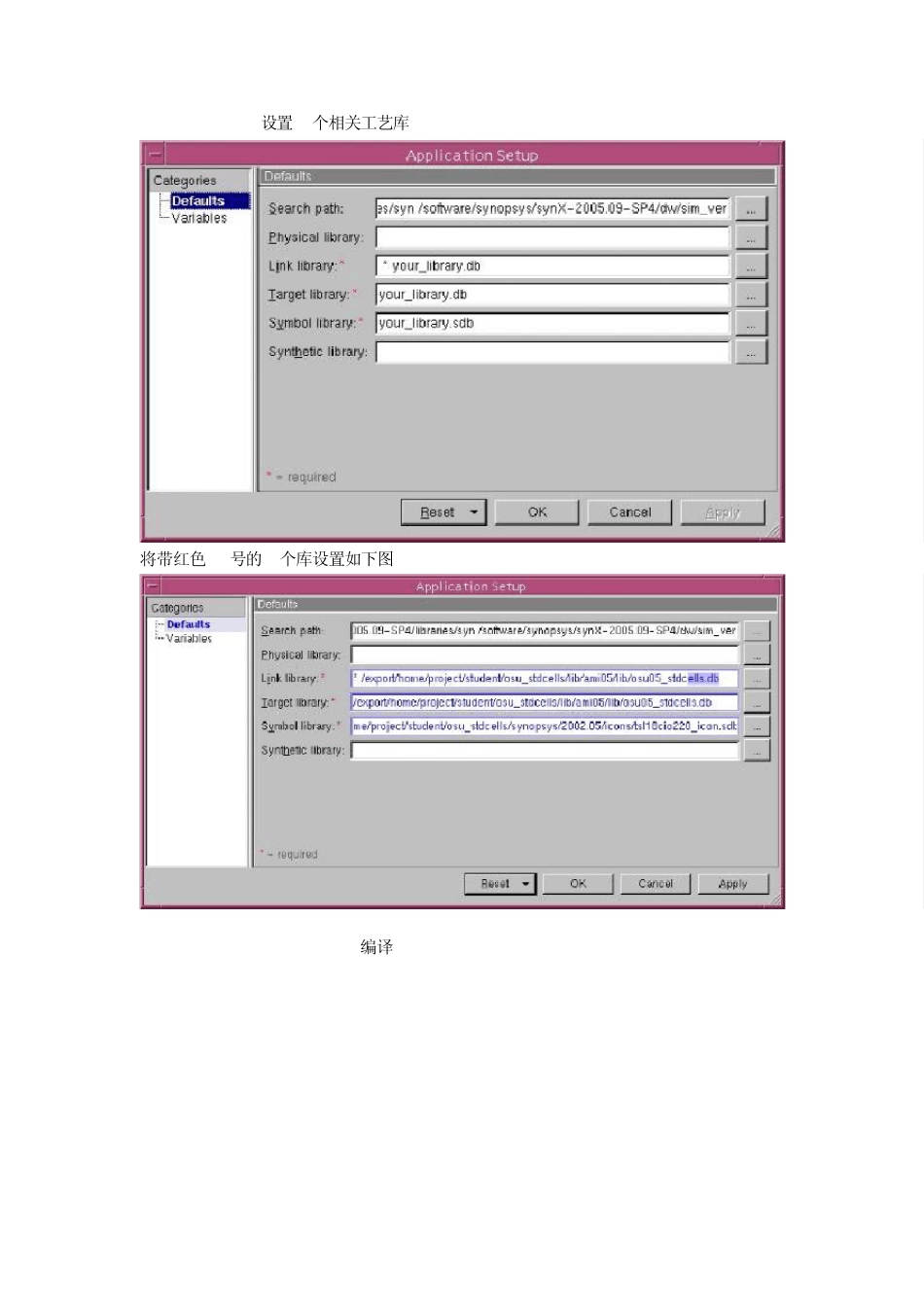

设置3个相关工艺库将带红色*号的3个库设置如下图Design->CompileDesign

编译Schematic->NewDesignSchematicView

可以看到综合后的顶层结构通过双击 C1模块 还可以看到全加器的门级结构为了后面自动布局布线的需要,这里我们要将这个综合结果保存为adder8_nl

在 psyn_gui-xg-t>后输入如下命令下面进行自动布局布线(一下有路径出现的地方要特别注意)打开SiliconEnsemble(sedsm&)File->Import->LEF…导入库的转换格式注意此文件的路径

File->Import->Verilog…导入工艺库(此库为 verilog描述的标准单元,包含各种延时信息)这里去掉后面的

继续File->Import->Verilog…导入网表adder8_nl

v(此处要先删掉第一个工艺库)这里要加上顶层模块名 adder8Floorplan->InitializeFloorplan…