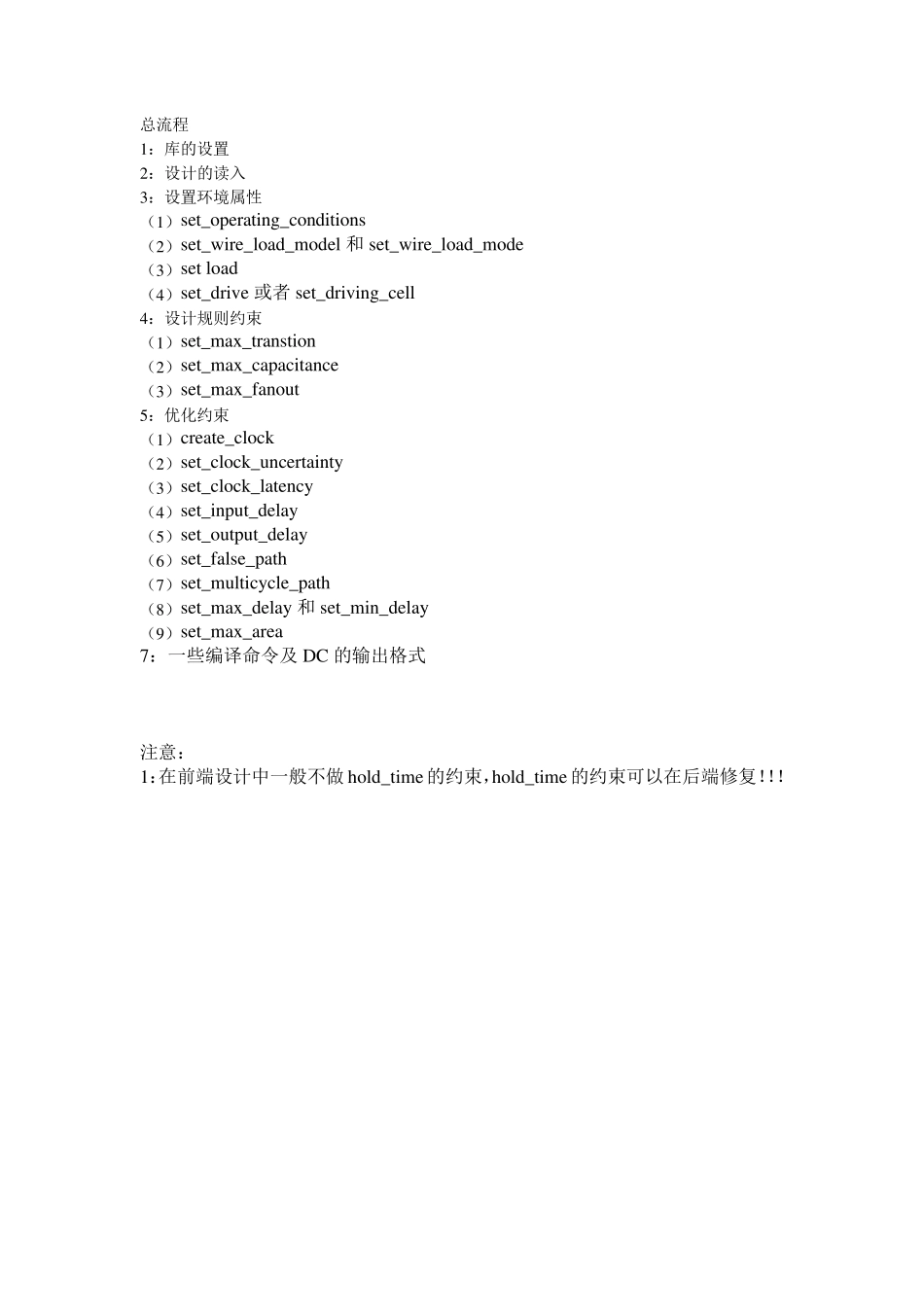

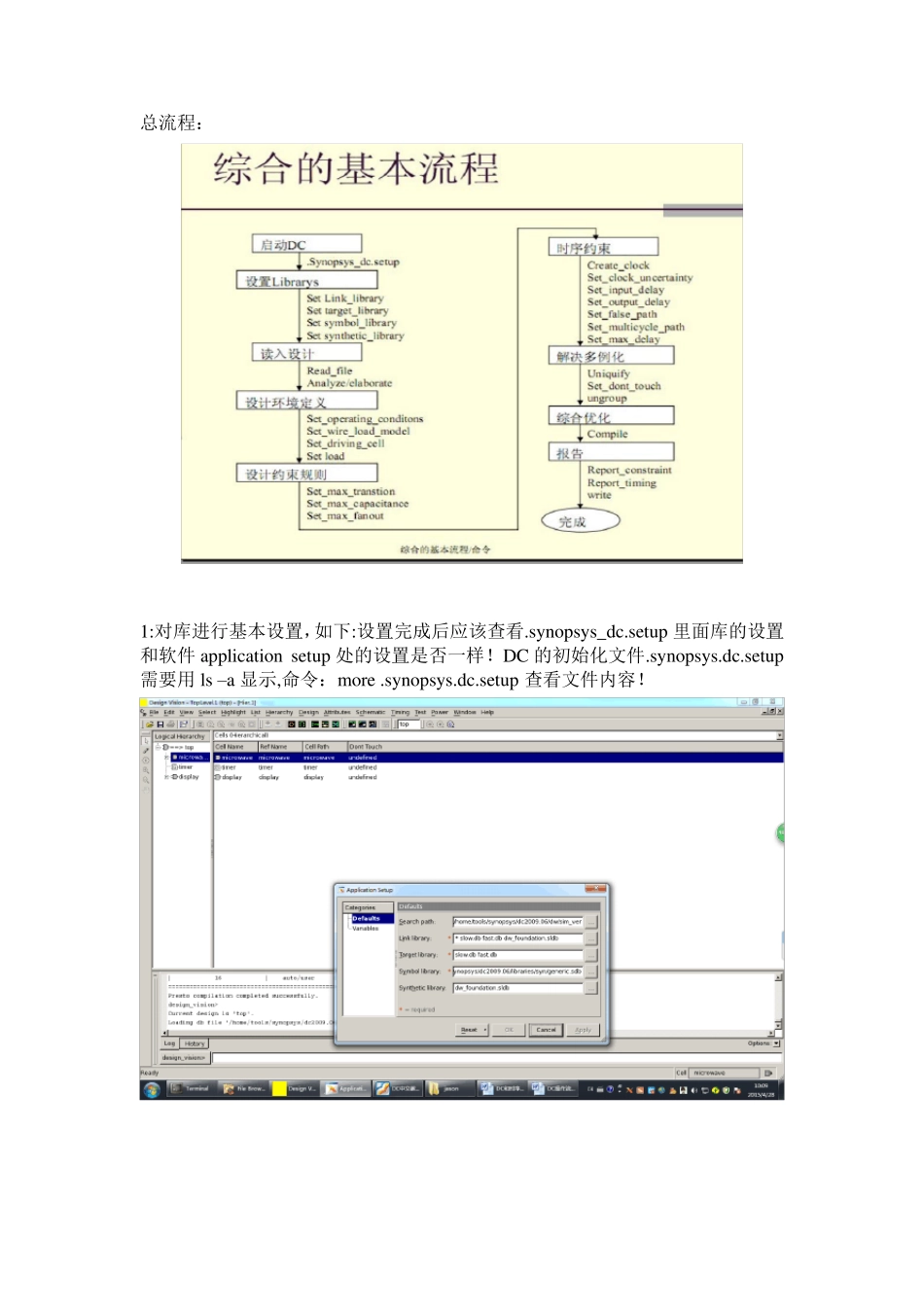

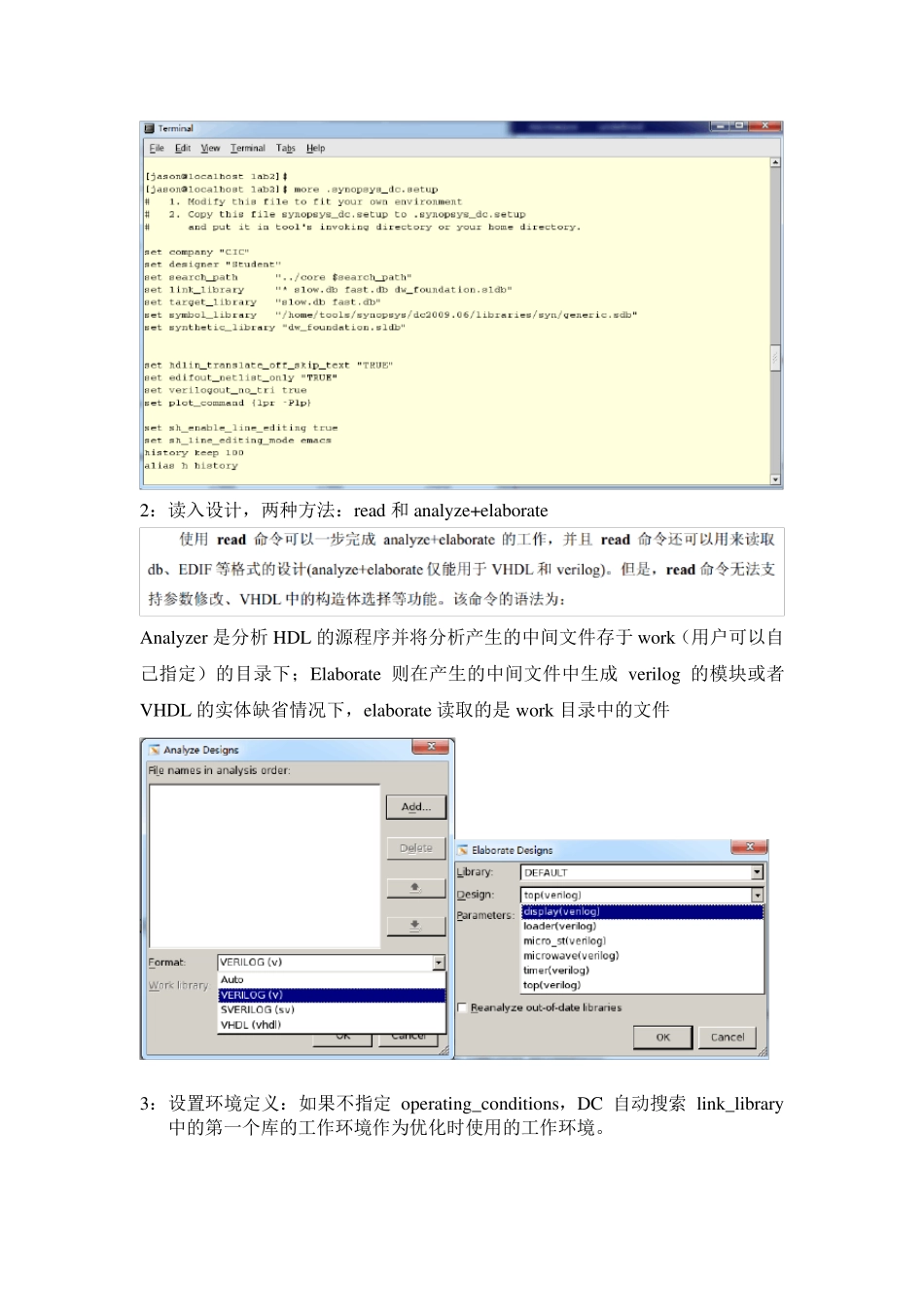

总流程 1:库的设置 2:设计的读入 3:设置环境属性 (1)set_operating_conditions (2)set_wire_load_model 和set_wire_load_mode (3)set load (4)set_drive 或者set_driving_cell 4:设计规则约束 (1)set_max_transtion (2)set_max_capacitance (3)set_max_fanout 5:优化约束 (1)create_clock (2)set_clock_uncertainty (3)set_clock_latency (4)set_input_delay (5)set_output_delay (6)set_false_path (7)set_multicycle_path (8)set_max_delay和set_min_delay (9)set_max_area 7:一些编译命令及 DC 的输出格式 注意: 1:在前端设计中一般不做 hold_time 的约束,hold_time 的约束可以在后端修复!!! 总流程: 1:对库进行基本设置,如下:设置完成后应该查看.sy nopsy s_dc.setu p 里面库的设置和软件application setu p 处的设置是否一样!DC 的初始化文件.sy nopsy s.dc.setu p需要用 ls –a 显示,命令:more .sy nopsy s.dc.setu p 查看文件内容! 2:读入设计,两种方法:read 和analyze+elaborate Analyzer 是分析HDL 的源程序并将分析产生的中间文件存于work(用户可以自己指定)的目录下;Elaborate 则在产生的中间文件中生成verilog 的模块或者VHDL 的实体缺省情况下,elaborate 读取的是work 目录中的文件 3:设置环境定义:如果不指定operating_conditions,DC 自动搜索link_library中的第一个库的工作环境作为优化时使用的工作环境。 (1) set_operating_conditions:工作条件包括三方面—温度、电压以及工艺;工作条件一般分三种情况:best case, typical case, worst case 图形界面: #1:先进入 the symbol view of the top 界面,选择 top 模块 #2:attributes—operating environment—operating conditions 命令方式: #1:可通过 report_lib libraryname 命令来查看,如下图查看的是 slow.db库的工作条件,则使用命令:report_lib slow,右边是 report_lib fast。 另外一个例子,只是为了说明库中的 library name 必须是用 report_lib 命令得到下面图形中的 conditions 里面的库的 name:(******自己想的******) #2:一般综合时候只需考虑最差和最好两种情况即可,最差情况用于做建立时间(setup time)的时序分析,最好情况用于做保持时间(hold time)的时序分析。最差...