- 1 - 1 DRAM 简介 动态存储器DRAM(Dynamic Random Access Memory)利用MOS 电容来保存信息,使用时不断给电容充电才能使信息保持

与静态存储器SRAM 相比,DRAM 的优点是:集成度高,功耗小,价格低,主要用于大容量存储器;DRAM 的缺点是:速度慢,需要刷新的控制电路

DRAM 分为普通DRAM 和SDRAM

本文介绍的HM5118165B 系列是属于普通DRAM中的EDO DRAM

它用EDO 页面模式作为高速存取模式

本节先介绍普通DRAM 的原理和时序关系

1 DRAM 结构 为了减少封装引脚数,地址分两批送至存储器

先送行地址,后送列地址

DRAM 的结构如下图所示

行时钟发生器列时钟发生器写时钟发生器RAS#CAS#WE#列地址锁存器行地址锁存器存储阵列行地址译码器列地址译码器行时钟列时钟I/O控制输出缓存列时钟输出缓存DoDIA0~A9 1

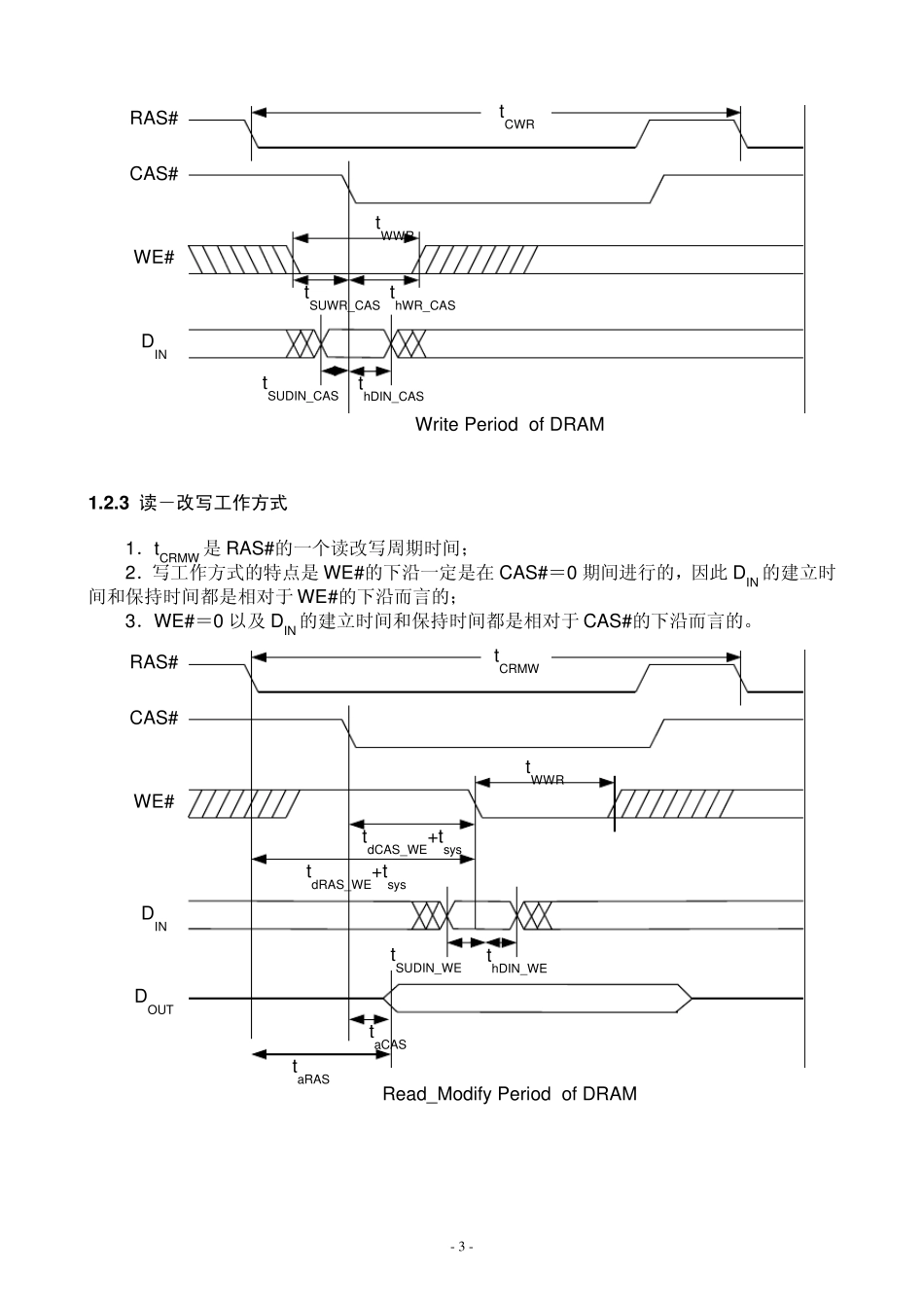

2 DRAM 工作方式 DRAM 有读、写、读-改写、页面和刷新等工作方式

其中RAS#1,CAS#与地址Addr的关系必须满足下面的条件,示意图如下

1.CAS#的下沿必须滞后于RAS#的下沿; 2.RAS#、CAS#的正负电平宽度分别应大于规定值; 3.行地址对 RAS#和列地址对 CAS#均应有足够的地址建立时间和保持时间

1 #表示该信号为低电平有效,下同

- 2 - tw RASLtw RASHtw CASHtw CASLRAS#CAS#tdRAS_CASAddrtSUAdrr_RAS tSUAdrr_CASthAdrr_RASthAdrr_CAS 1

1 读工作方式 1.tCRD 是RAS#的一个读周期时间; 2.读命令(WE#)的建立时间和保持时间是相对于CAS#的; 3.有两个读出时间:相对于RAS#下沿和CAS#下沿

tCRDRA