第10 章 DSP Bu ilder 设计深入 应用Matlab/DSP Bu ilder 可以对多种类型的电子线路模块或系统进行建模、分析和硬件实现,且更擅长于一些较复杂的功能系统,及偏向于高速算法方面的模块的设计和实现,还能利用HDL Import 模块将 HDL 文本设计转变成为 DSP Bu ilder 元件

本章将给出一些 DSP 及数字通信领域中实用模块的设计实例,以及基于 Matlab/DSP Bu ilder 平台的IP 核的应用

1 FIR 数字滤波器设计 FIR(Finite Impu lse Response:有限冲激响应)滤波器在数字通信系统中,被大量用于以实现各种功能,如低通滤波、通带选择、抗混叠、抽取和内插等

在 DSP Bu ilder 的实际应用中,FIR 滤波器是最为常用的模块之一

DSP Bu ilder 的FIR滤波器设计方式有多种,作为示例,本节介绍基于模块的FIR 与基于 IP 的FIR 设计方法

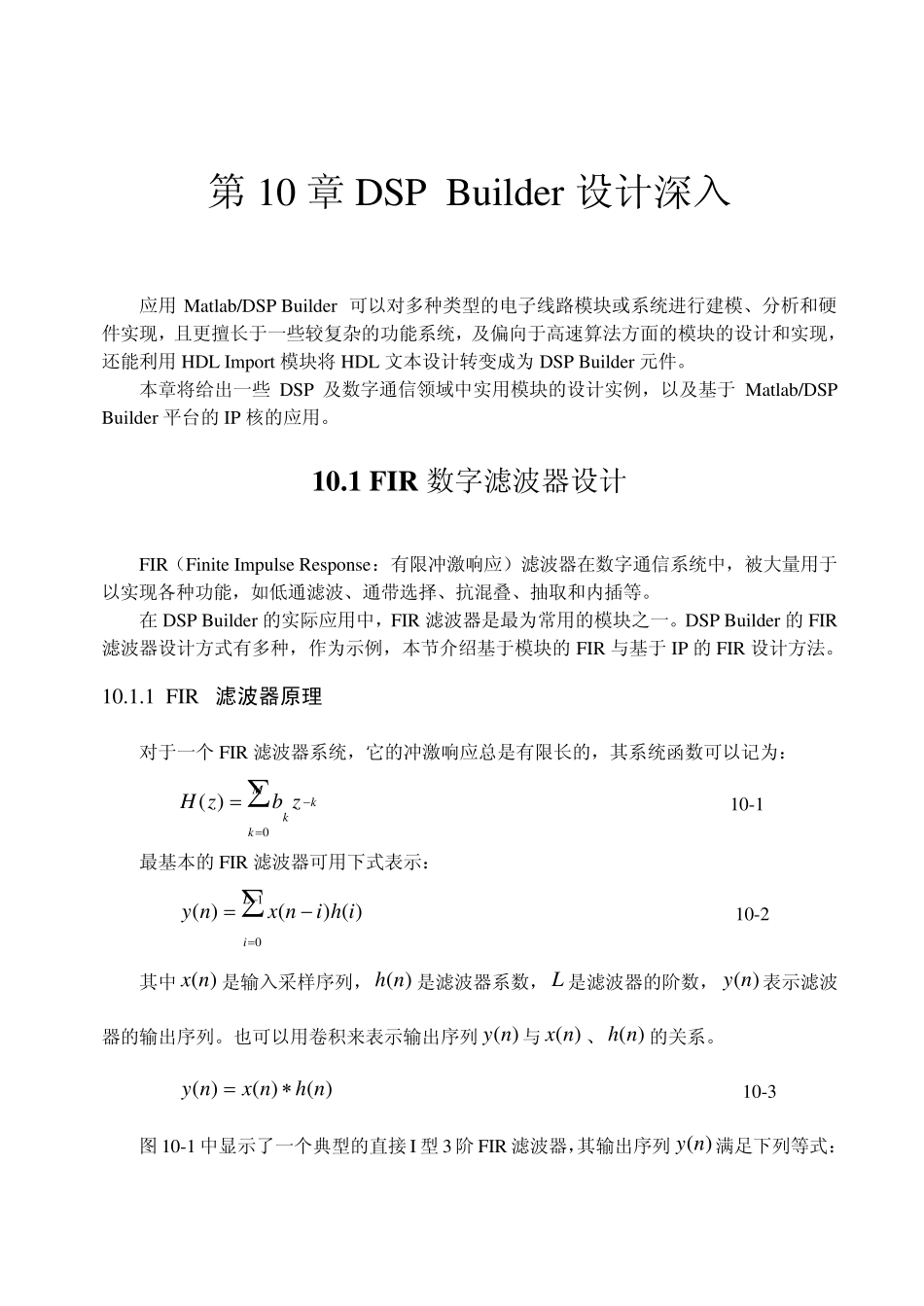

1 FIR 滤波器原理 对于一个 FIR 滤波器系统,它的冲激响应总是有限长的,其系统函数可以记为: ∑=−=Mkkk zbzH0)( 10-1 最基本的FIR 滤波器可用下式表示: ∑−=−=10)()()(Liihinxny 10-2 其中 ( )x n 是输入采样序列, ( )h n 是滤波器系数, L 是滤波器的阶数,)(ny表示滤波器的输出序列

也可以用卷积来表示输出序列)(ny与)(nx、)(nh的关系

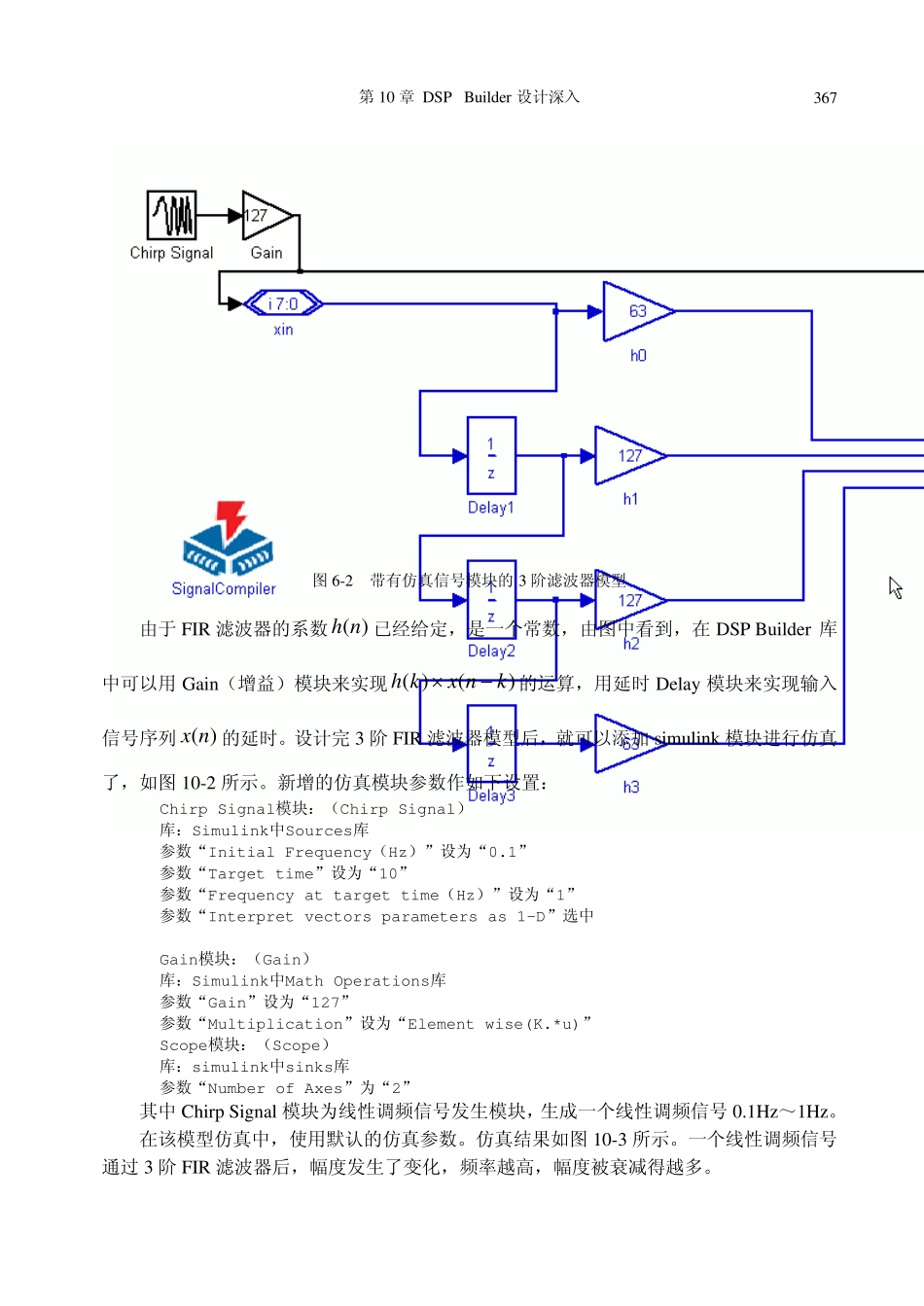

)()()(nhnxny∗= 10-3 图 10-1 中显示了一个典型的直接 I 型3 阶 FIR 滤波器,其输出序列)(ny满足下列等式: EDA 技术与VHDL 366)3()3()2()2()1()1()()0()(−+−+−+=nxhnxhnxhnxhnh 10-4 在这个FIR 滤波器中,总