燕 山 大 学EDA 课程设计报告书题目: 自动打铃器 姓名: 班级: 电子信息工程 4 班 学号: 成绩: (注:此文件应以同学学号为文件名)一、设计题目及要求题目:自动打铃器要求:1.有数字钟功能;(不包括校时等功能)2.可设置六个时间,定时打铃;下载后可任意编辑3.响铃 5 秒钟

二、设计过程及内容1、总体设计思路(1)使电路有计时功能,分别利用两个十进制 74160 设置成六十进制和二十四进制计数器

用已经设计完成的两个六十进制和一个二十四进制计数器进位连接完成时,分,秒的计数功能(2)用三个 74160 设置成 366 进制的计数器,并将这个 366 进制的计数器设置成分频器得到 1hz 的时钟脉冲作为开始的输入信号

(3)四个八选一数字选择器和 7449 译码器设计成电路完成数字显示功能,用一个八进制计数器控制实验箱上的八个数码管

(4)连接有计数功能的模块的相应输出端设置六个时间,通过与门和非门,连接到响铃模块的输入端以控制其响铃

全天计数器的输出端与扫描显示电路输入端对应连接

(5)一个 D 触发器和一个五进制计数器做成响铃五秒的响铃电路

最后将以上设计的五个模块连接起来,组成自动打铃器

2、设计过程该自动打铃器由五部分构成,分别为分频电路、数字钟电路、扫描显示电路、设定时间电路、响铃电路

第一部分 分频电路分频电路是为了对 732Hz 脉冲进行分频,得到 1Hz 的脉冲信号

该模块由三片 74160 芯片级联构成 732 进制计数器,采纳整体置 0 法

输出频率为 1Hz 的信号,为数字钟提供脉冲

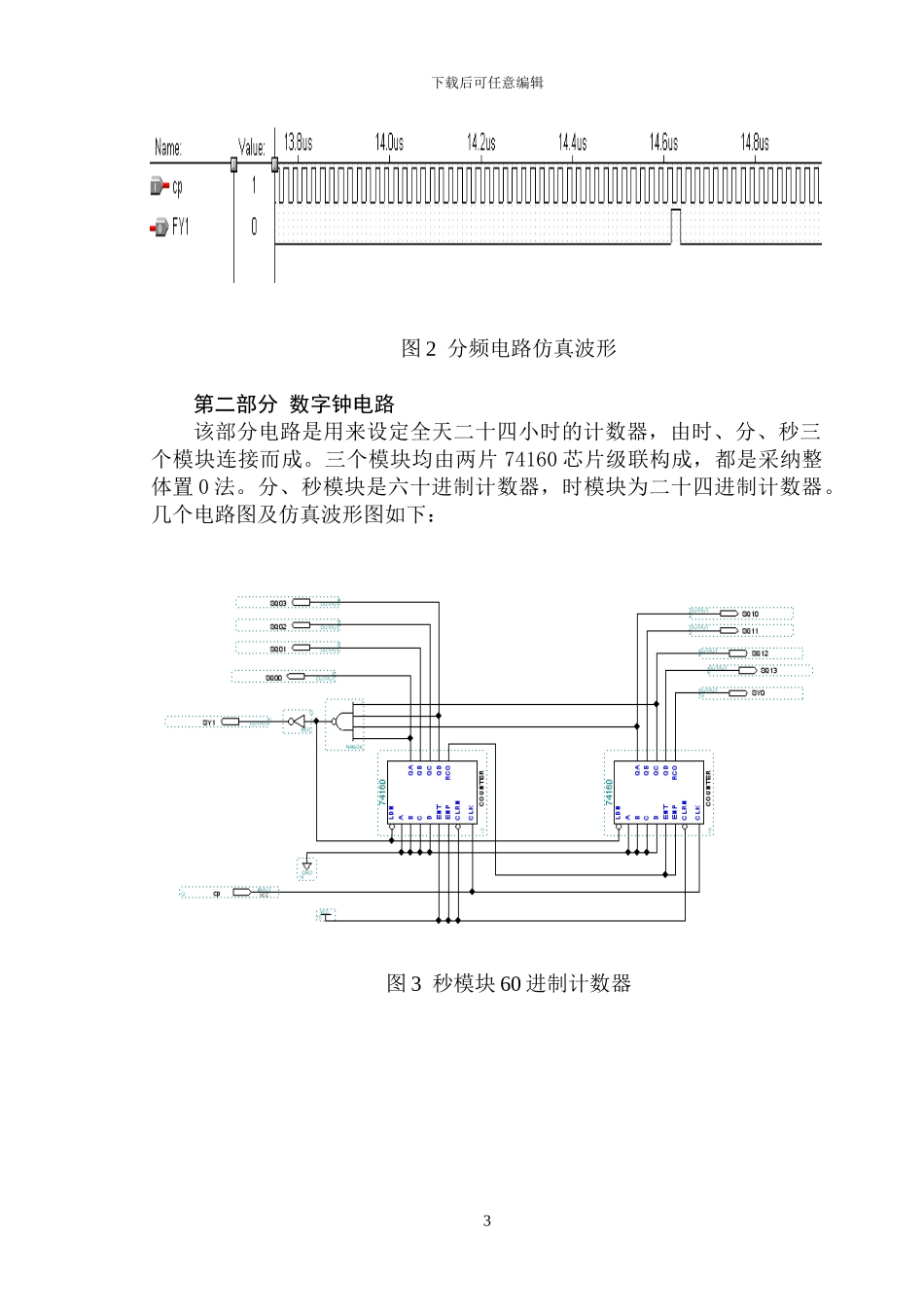

电路图如下图 1 分频电路电路图对分频电路进行仿真,所得仿真波形如图 2:2下载后可任意编辑图 2 分频电路仿真波形第二部分 数字钟电路该部分电路是用来设定全天二十四小时的计数器,由时、分、秒三个模块连接而成

三个模块均由两片 74160 芯片级联构成,都是采纳