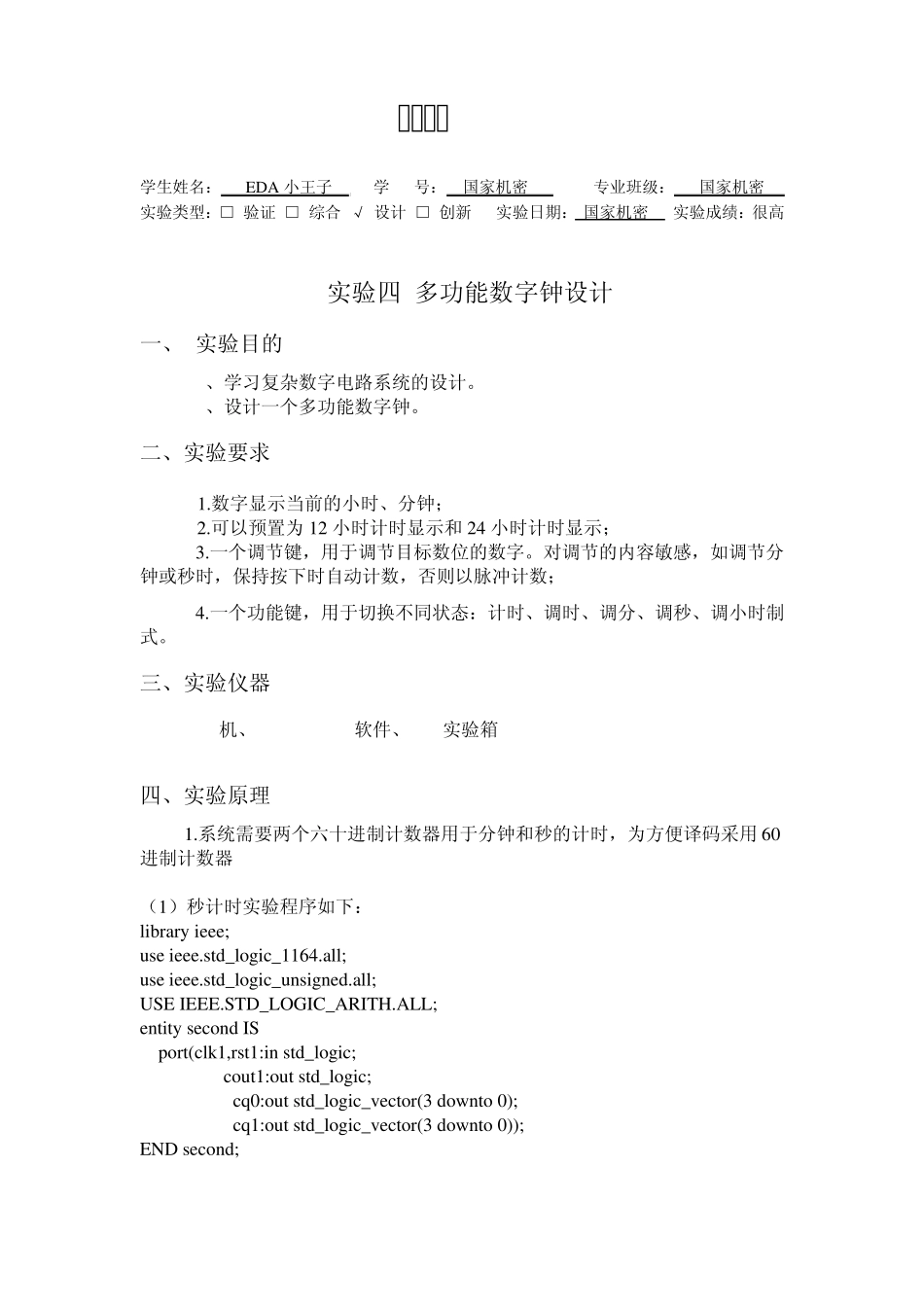

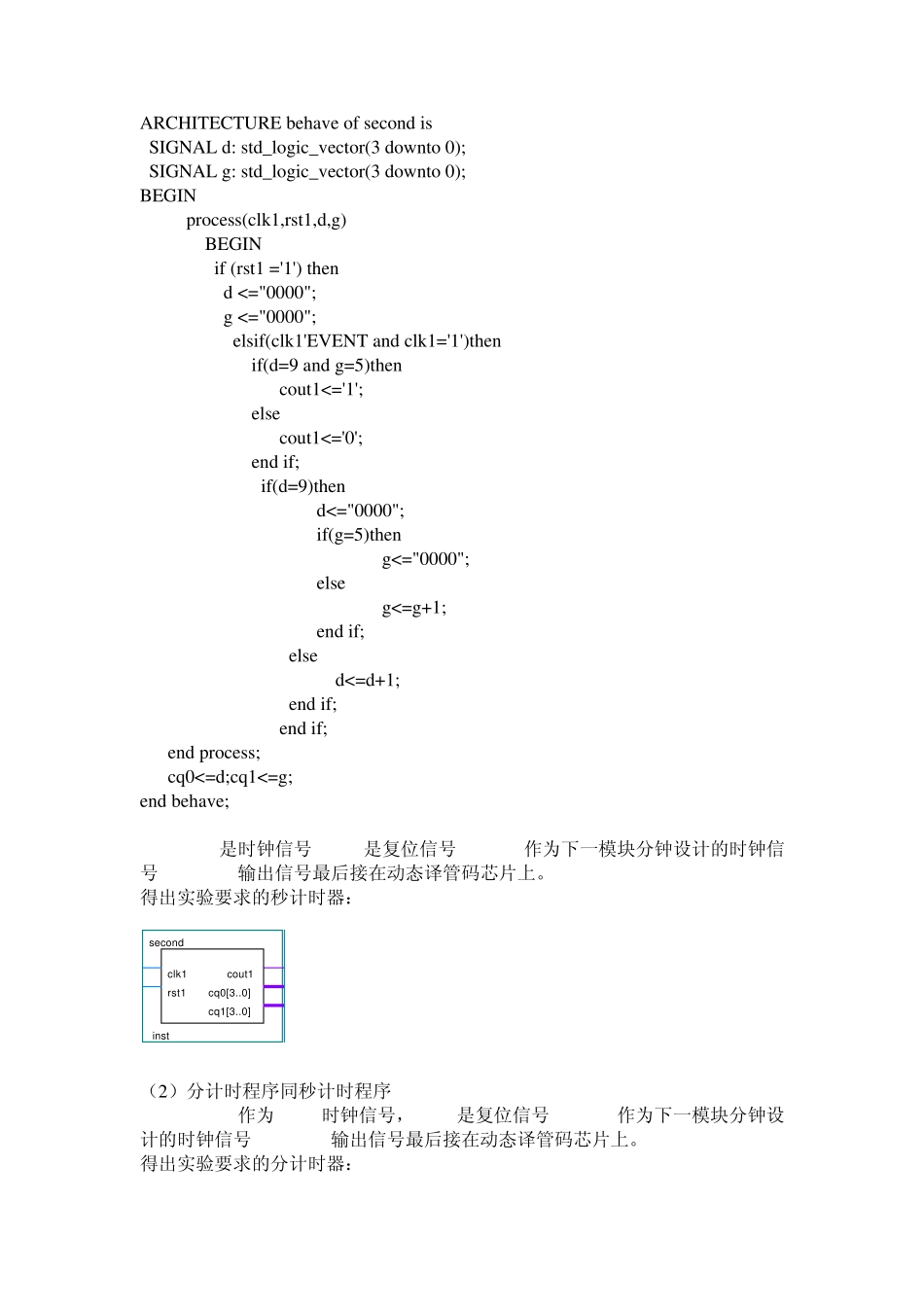

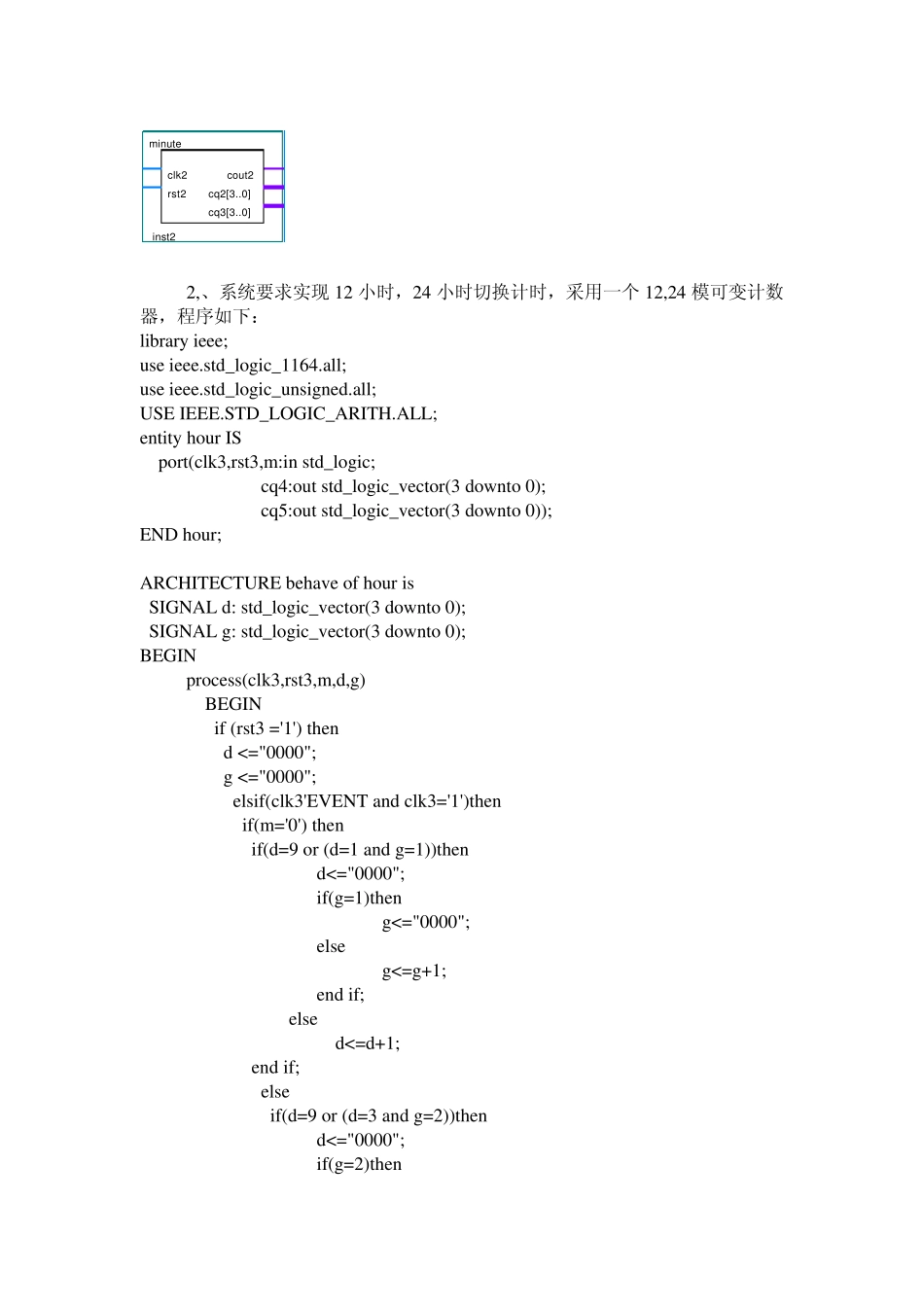

实验报告 学生姓名: EDA 小王子 学 号: 国家机密 专业班级: 国家机密 实验类型:□ 验证 □ 综合 √ 设计 □ 创新 实验日期: 国家机密 实验成绩:很高 实验四 多功能数字钟设计 一、 实验目的 1、学习复杂数字电路系统的设计。 2、设计一个多功能数字钟。 二、实验要求 1.数字显示当前的小时、分钟; 2.可以预置为 12 小时计时显示和 24 小时计时显示; 3.一个调节键,用于调节目标数位的数字。对调节的内容敏感,如调节分钟或秒时,保持按下时自动计数,否则以脉冲计数; 4.一个功能键,用于切换不同状态:计时、调时、调分、调秒、调小时制式。 三、实验仪器 PC机、Quartus II软件、EDA实验箱 四、实验原理 1.系统需要两个六十进制计数器用于分钟和秒的计时,为方便译码采用 60 进制计数器 (1)秒计时实验程序如下: library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; USE IEEE.STD_LOGIC_ARITH.ALL; entity second IS port(clk1,rst1:in std_logic; cout1:out std_logic; cq0:out std_logic_vector(3 downto 0); cq1:out std_logic_vector(3 downto 0)); END second; ARCHITECTURE behave of second is SIGNAL d: std_logic_vector(3 dow nto 0); SIGNAL g: std_logic_vector(3 dow nto 0); BEGIN process(clk1,rst1,d,g) BEGIN if (rst1 ='1') then d <="0000"; g <="0000"; elsif(clk1'EVENT and clk1='1')then if(d=9 and g=5)then cout1<='1'; else cout1<='0'; end if; if(d=9)then d<="0000"; if(g=5)then g<="0000"; else g<=g+1; end if; else d<=d+1; end if; end if; end process; cq0<=d;cq1<=g; end behave; clk1是时钟信号,rst1是复位信号, cout1作为下一模块分钟设计的时钟信号,cq0,cq1输出信号最后接在动态译管码芯片上。 得出实验要求的秒计时器: (2)分计时程序同秒计时程序 cout1作为clk2时钟信号,rst2是复位信号, cout2作为下一模块分钟设计的时钟信号,cq2,cq3输出信号最后接在动态译管码芯片上。 得出实验要求的分计时器: clk1rst1cou t1cq0[3..0]cq1[3..0]secondinst 2,、系统要求实现 12 小时,24 小时切换计时,采用一个 12,24 模可变计数器,程序如下: library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_un...