Paper ET3

1 INTERNATIONAL TEST CONFERENCE 1 978-1-4244-4867-8/09/$25

00 ©2009 IEEE Doing More with Less – An IEEE 1149

7 Embedded Tutorial : Standard for Reduced-pin and Enhanced-functionality Test Access Port and Boundary-Scan Architecture Adam W Ley ASSET InterTech, Inc

Richardson TX, USA Abstract IEEE Std 1149

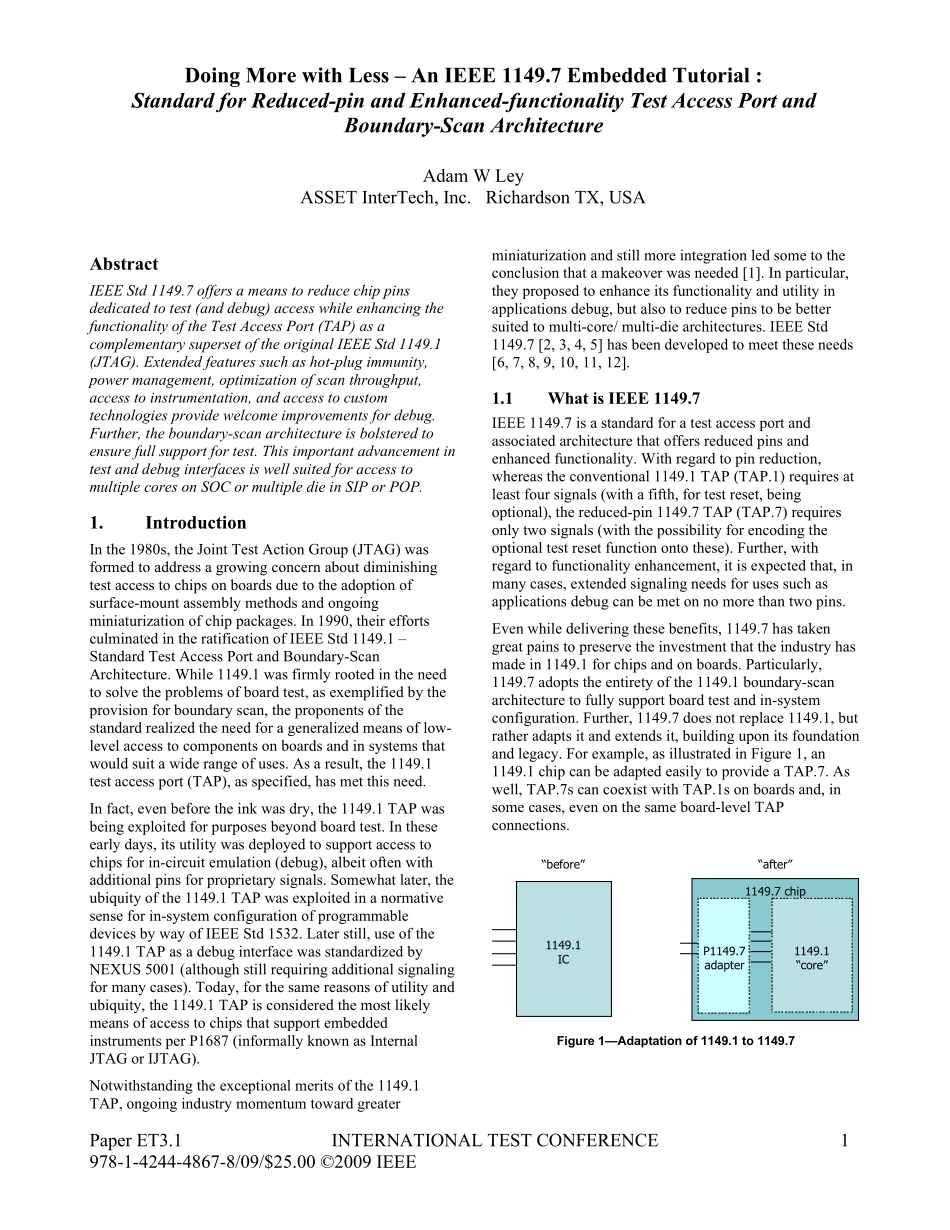

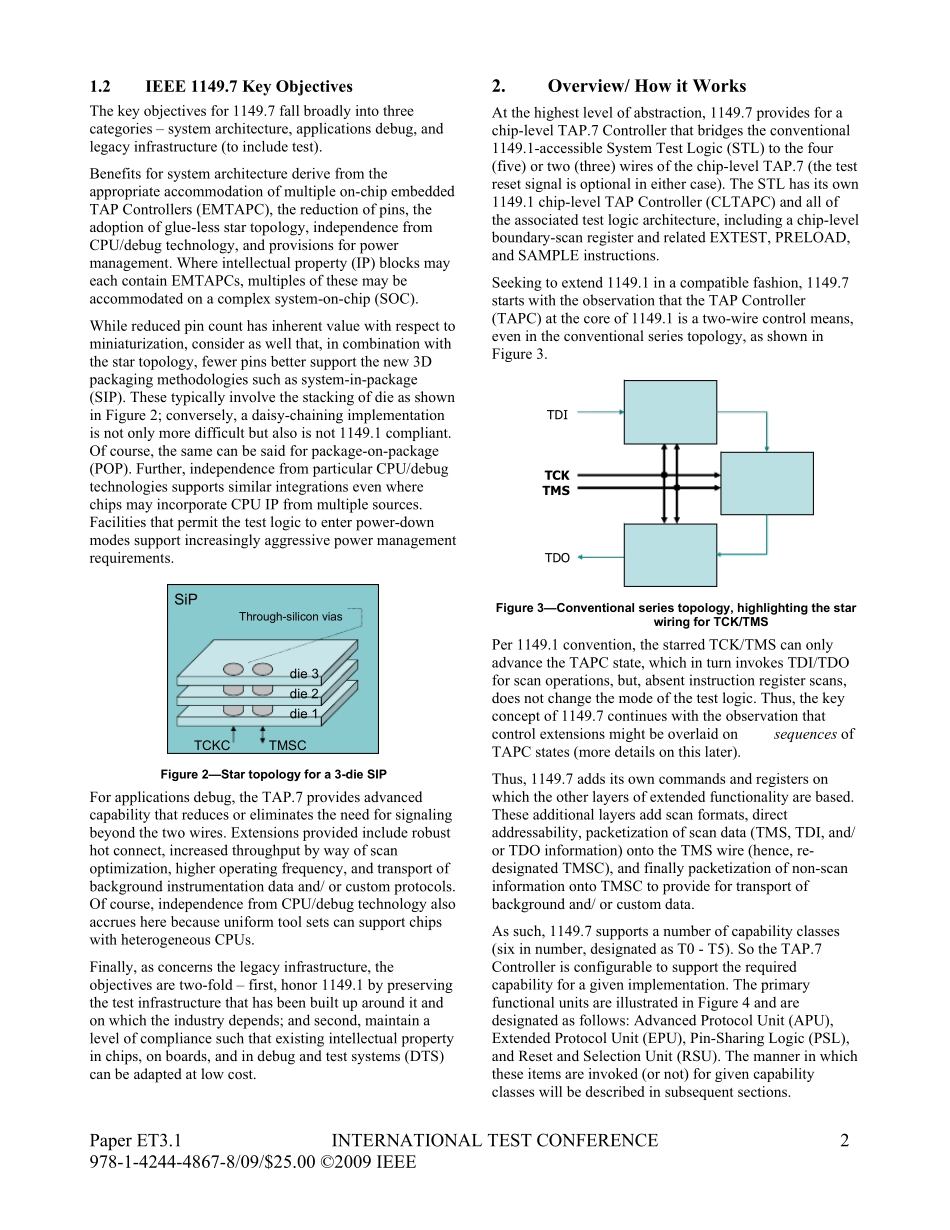

7 offers a means to reduce chip pins dedicated to test (and debug) access while enhancing the functionality of the Test Access Port (TAP) as a complementary superset of the original IEEE Std 1149

1 (JTAG)

Extended features such as hot-plug immunity, power management, optimization of scan throughput, access to instrumentation, and access to custom technologies provide welcome improvements for debug

Further, the boundary-scan architecture is bolstered to ensure full support for t