七人表决器设计 一

设计要求 1

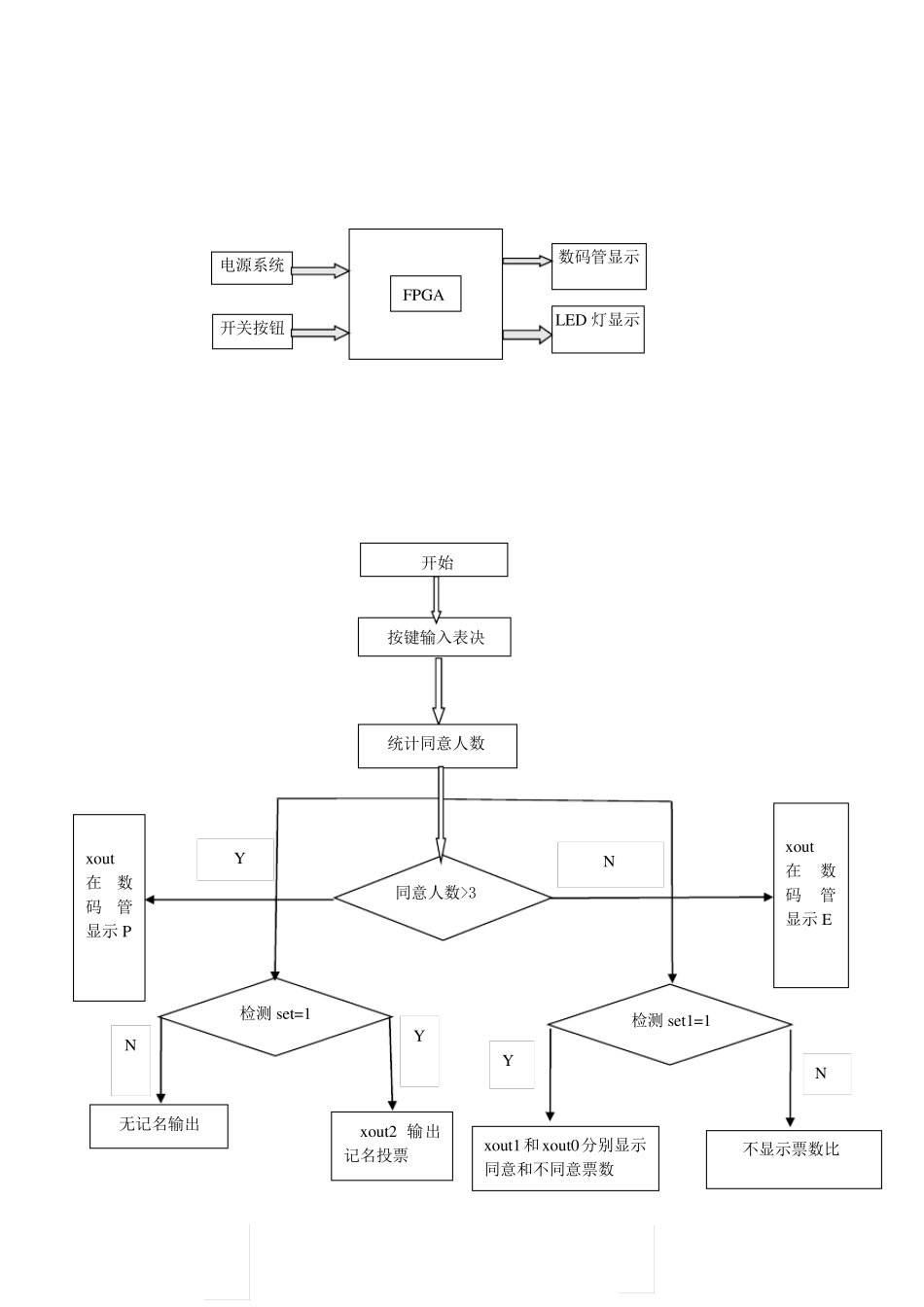

能够完成七人表决的功能,并且直观的显示结果:决议通过显示字母P,否则显示 字母E; 2

能够选择显示表决双方的人数,有控制开关与显示指示灯,并且能够实时的显示反对与赞成的人数; 3

能够选择是否记名,并有指示灯显示

当选择记名时,与表决参与者相对应的指示灯亮起; 4

不设置弃权的状况,超过三人同意则表示决议通过

设计思路 1

使用Altera 的Cy clone II 器件,FPGA 型号为 EP2C35F672C6N;开发平台为Qu artu s II 8

使用 6 个拨动开关用以进行表决,开关闭合时表示同意,断开时表示不同意; 3

使用 6 个 LED 用以显示表决的个人结果,用以显示记名时的情况

LED 亮起表示表决人同意,否则表示不同意; 4

使用一个七段数码管用以显示表决结果,通过显示P,否则显示E;另外使用两个数码管用以分别显示同意与不同意的人数; 5

使用两个拨动开关控制是否记名,是否显示表决的人数结果; 6

其他电路按需要搭建

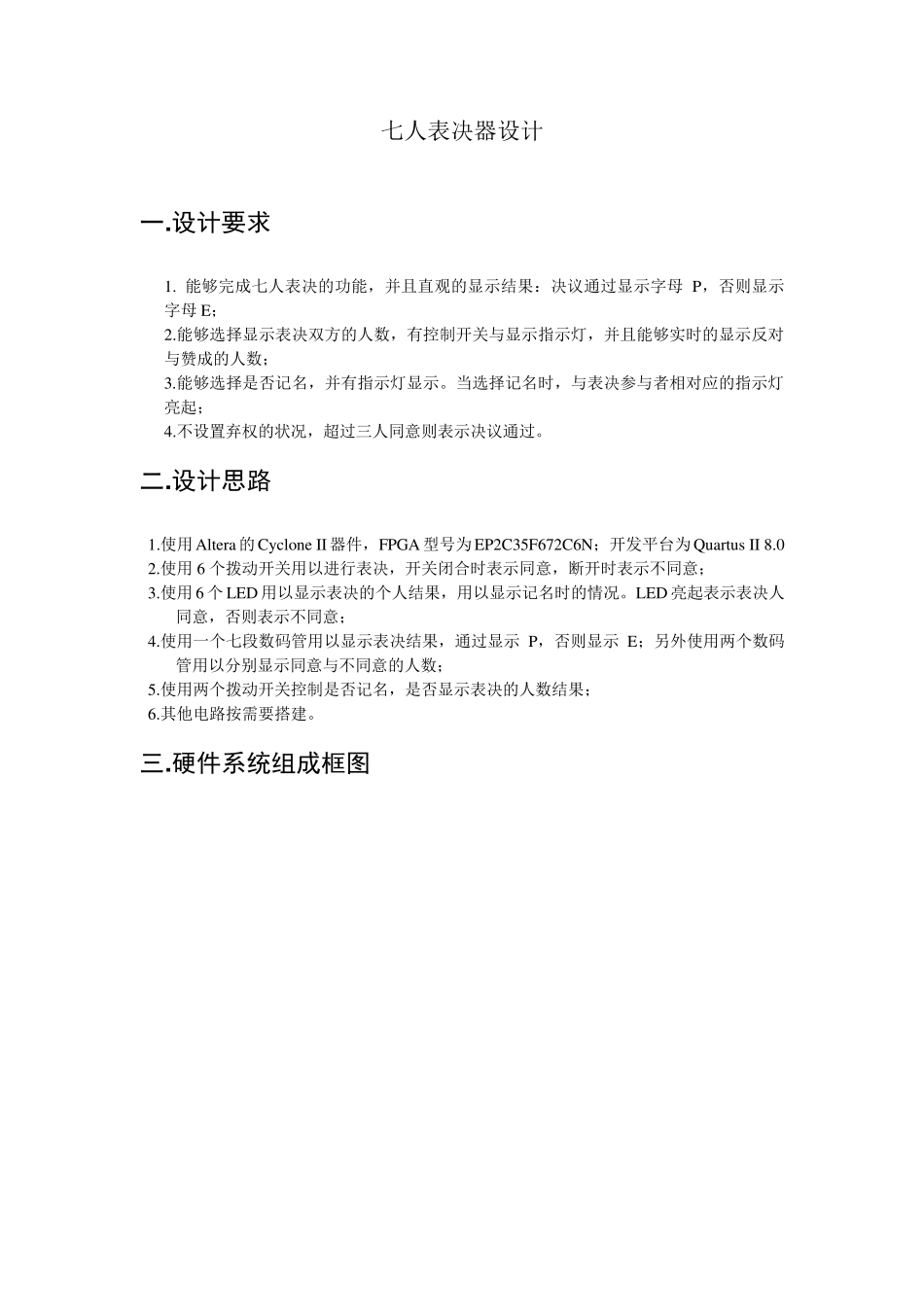

硬件系统组成框图 FPGA 数码管显示 LED 灯显示 开关按钮 电源系统 开始 按键输入表决 同意人数>3 统计同意人数 x ou t 在数码管显示P Y x ou t 在 数码 管显示E N 检测set=1 检测set1=1 x ou t2 输出记名投票 x ou t1和x ou t0分别显示同意和不同意票数 Y Y 无记名输出 N 不显示票数比 N 注释:set:选择是否记名 set1:选择是否显示投票人数及比例 x in[0:6]:表决输入,分别是七个拨动开关 sel:输出指示是否记名投票 sel1:输出指示是否显示投票人数及比例 x ou t[0:6]:译码用数码管输出表决是否通过 x ou t0[0:6]:译码用数码管输出同意的人数(set1=1) x ou t1[0