数字频率计设计 一、实验目的 1

熟悉 CPLD 的开发软件的基本使用

理解频率计的测量原理

掌握 CPLD 逻辑电路设计方法

掌握虚拟数字频率计的软件设计

二、实验任务和内容 1

在 CPLD 中设计一个数字频率计电路,设计要求为: 测量范围:1Hz~1MHz, 分辨率, 数码管动态扫描显示电路的 CPLD 下载与实现

使用 LabVIEW 进行虚拟频率计的软件设计

要求设计软件界面,闸门时间为4 档,1s,100ms,10ms,1ms,频率数字显示

3.使用设计虚拟逻辑分析仪软件和 CPLD 电路,进行软硬件调试和测试 三、实验器材 1

SJ-8002B 电子测量实验箱 1 台 2.计算机(具有运行 windows2000 和图形化控件的能力) 1 台 3.函数发生器 1 台 4

SJ-7002 CPLD 实验板 1块 5

短接线若干 四、实验原理 4

测频原理 所谓“频率”,就是周期性信号在单位时间变化的次数

电子计数器是严格按照 f=N/T 的定义进行测频,其对应的测频原理方框图和工作时间波形如图 1 所示

从图中可以看出测量过程:输入待测信号经过脉冲形成电路形成计数的窄脉冲,时基信号发生器产生计数闸门信号,待测信号通过闸门进入计数器计数,即可得到其频率

若闸门开启时间为 T、待测信号频率为 fx,在闸门时间T内计数器计数值为 N,则待测频率为 fx = N/T (1) 若假设闸门时间为 1s,计数器的值为 1000,则待测信号频率应为 1000Hz 或 1

000kHz,此时,测频分辨力为 1Hz

本实验的闸门时间分为为 4 档:1s,100ms,10ms,1ms

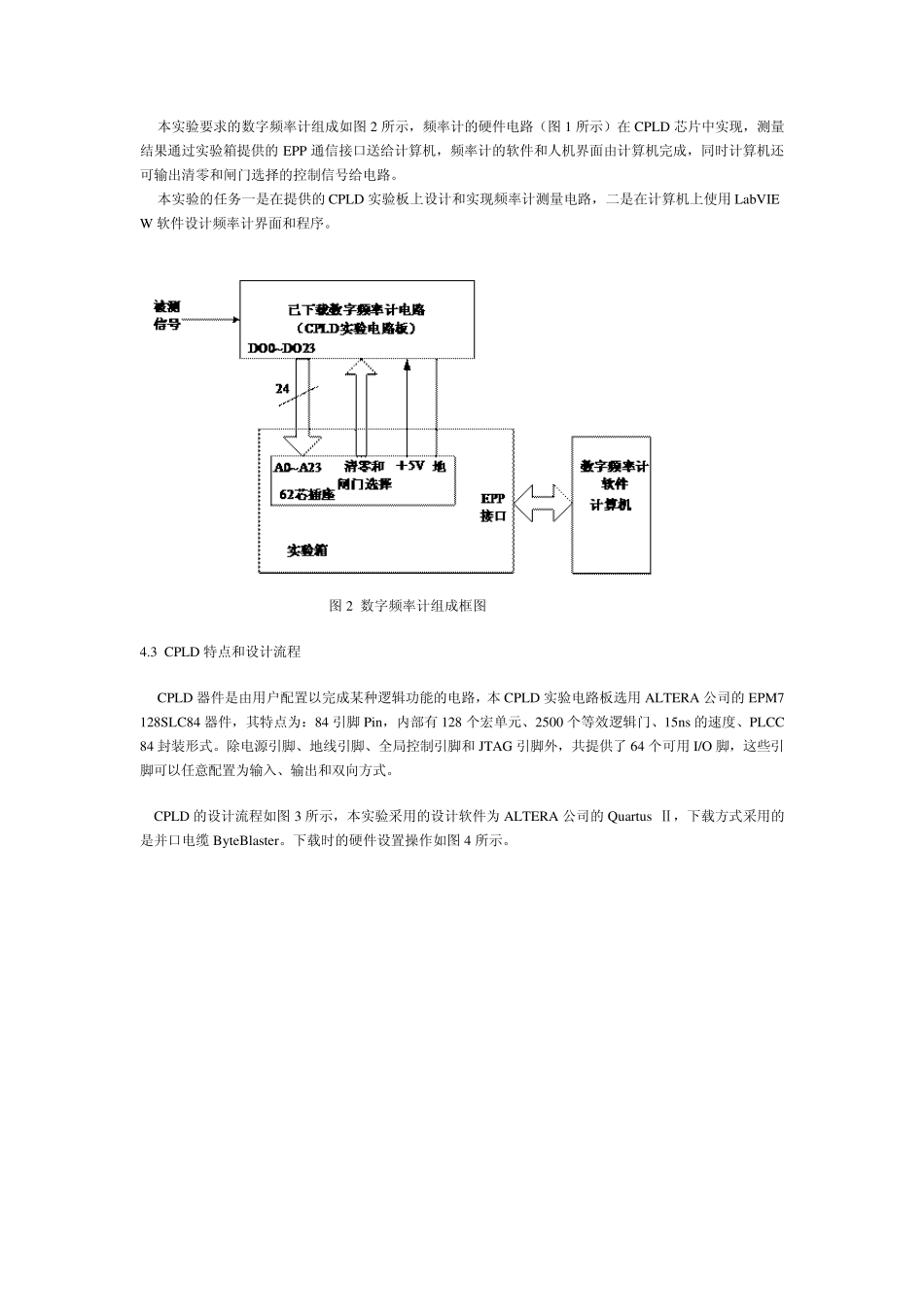

图 1 测频原理框图和时间波形 4 .2 数字频率计组成 本实验要求的数字频率计组成如图 2 所示,频率计的硬件电路(图 1 所示)在 CPLD 芯片中实现,测量