1 南航金城学院 数字电路实验课程设计报告 数字闹钟2 第一部分 设计任务 1

1 设计任务 设计、制作一个带有校时功能、可定时起闹的数字闹钟

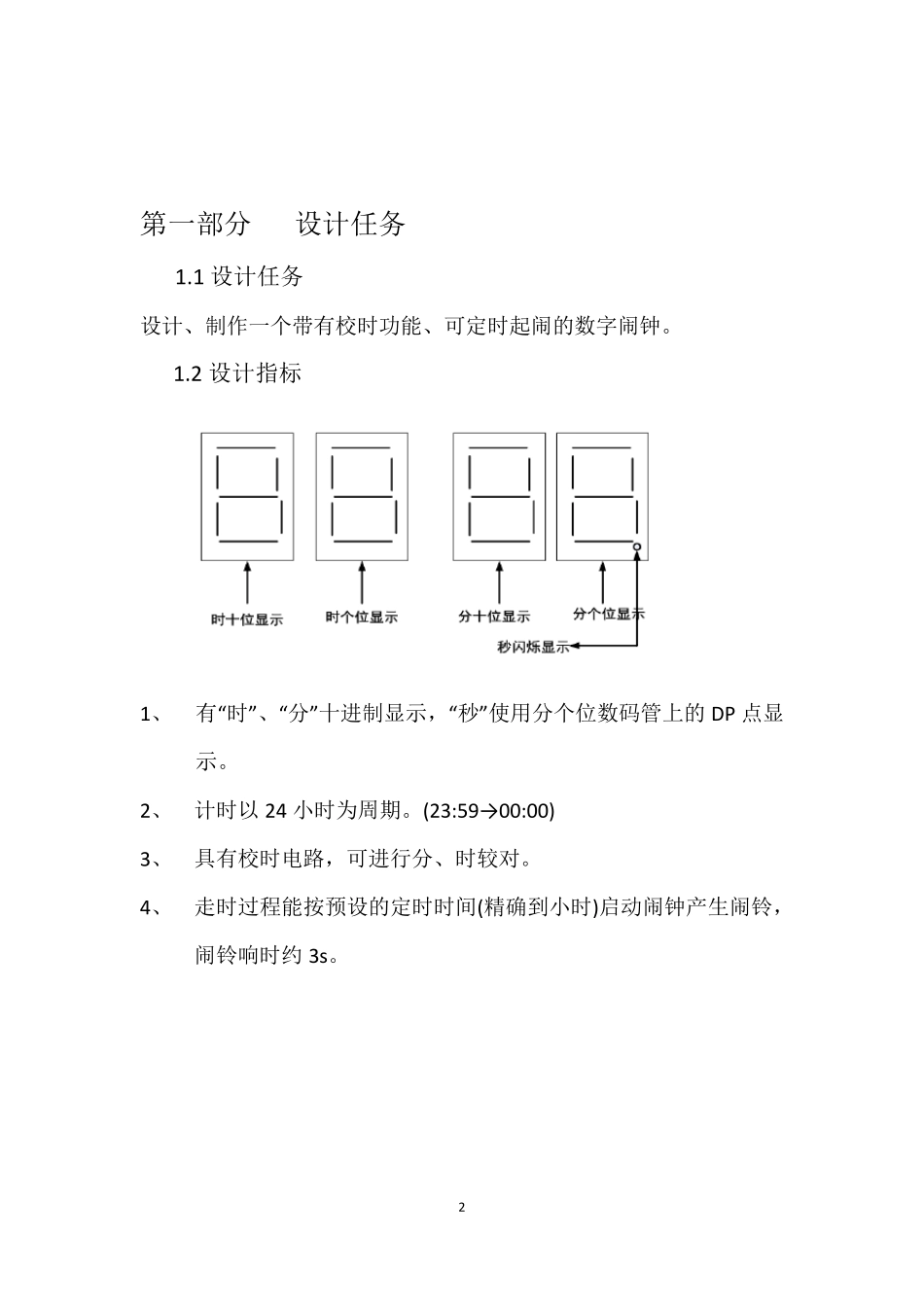

2 设计指标 1、 有“时”、“分”十进制显示,“秒”使用分个位数码管上的 DP 点显示

2、 计时以 24 小时为周期

(23:59→ 00:00) 3、 具有校时电路,可进行分、时较对

4、 走时过程能按预设的定时时间(精确到小时)启动闹钟产生闹铃,闹铃响时约 3s

3 第二部分 设计方案 2

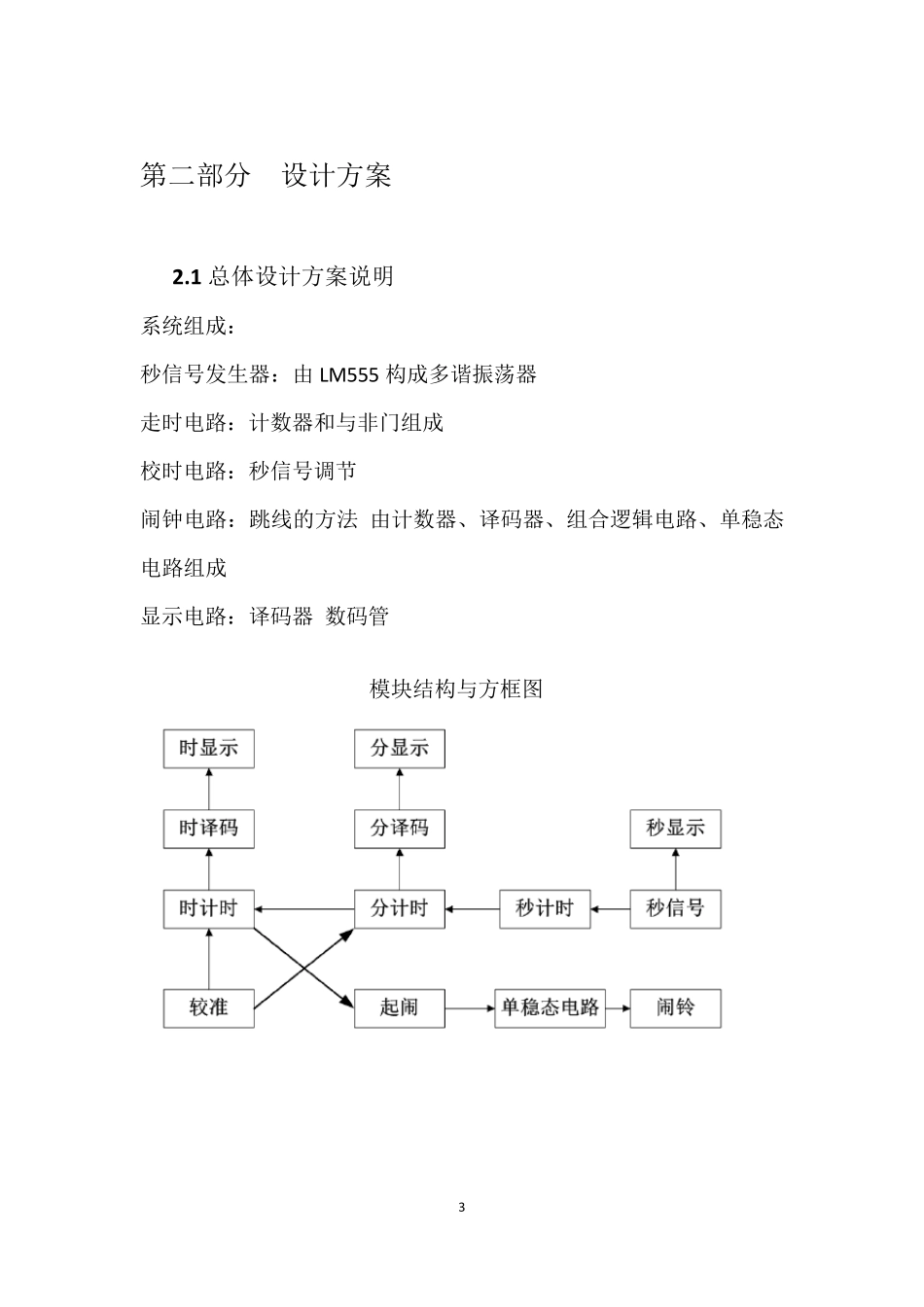

1 总体设计方案说明 系统组成: 秒信号发生器:由LM 555 构成多谐振荡器 走时电路:计数器和与非门组成 校时电路:秒信号调节 闹钟电路:跳线的方法 由计数器、译码器、组合逻辑电路、单稳态电路组成 显示电路:译码器 数码管 模块结构与方框图 4 第三部分 电路设计与器件选择 3

1 秒信号发生器 3

1 模块电路及参数计算 提供秒脉冲 取R1=1

5K,R2=2

4K C=220uF T≈1S 3

2 工作原理和功能说明 3

3 器件说明 内部电路组成: (1)分压器(3 个R) (2)电压比较器 (A1、A2) (3)RS 触发器 (4)反相器 (5)晶体管 T 1 端 GND 地 2 端 TR 低电平触发输入 3 端 UO 输出 4 端 RD 直接清 0 5 端 CV 电压控制,不用 时经 0

01F 电容 接地 6 端 TH 高电平触发输入 7 端 D 三极管集电极 8 端 VCC 电源(4

5V~18V) CRTCRRTPLPH2217

0z11HTfCRRTTTPLPH)2(7

021 5 3

2 走时电路设计 3

1 模块电路及参数计算 包括秒计时器、分计时器、时计时器,每一部分由两片计数器级联构成

秒计时器:十进制与六进制级联而成,由两片 74LS163