1 数字电路系统设计初步 —可预置计数器设计 一、 设计任务及要求 任务:设计一个可预置计数器

要求:最大计数范围是0~9,采用一位LED 数码管显示计数值;实际计数范围可通过开关输入预置,当计数达到预置值时停止计数

计数器同时具有复位清零的功能

二、基本原理 首先,从10 位拨码开关预置一个数(0—9)通过74LS148 及其他门电路进行编码,设编码后的4 位二进制为 A3A2A1A0

然后通过74LS86 和 74LS32 组成的比较器与 计数器74LS390 出 来 的4 位二进 制 B3B2B1B0 进 行 比 较

若A3A2A1A0>B3B2B1BO,则比较器输出为高电平即逻辑‘1‘使得门控 74LS00 打开,此时允许计数单脉冲通过,计数器开始对脉冲进行计数,且 B3B2B1B0 逐渐增大

当B3B2B1B0=A3A2A1A0 时,门控关闭,计数器不进行计数,数码管最终显示刚开始输入的数

整个工作过程中可随时按复位键 RESERT 对计数器进行清零

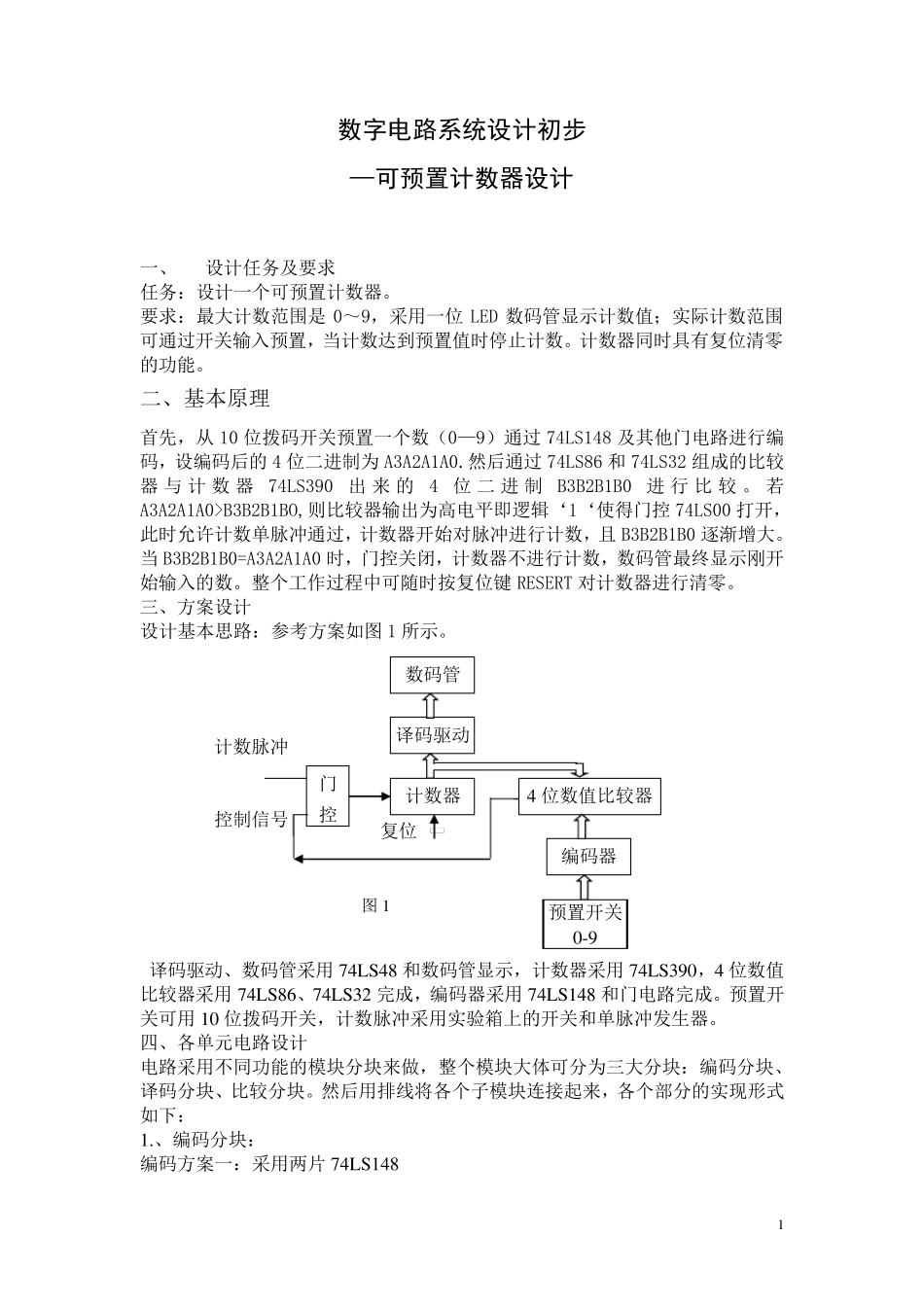

三、方案设计 设计基本思路:参考方案如图1 所示

译码驱动、数码管采用74LS48 和数码管显示,计数器采用74LS390,4 位数值比较器采用74LS86、74LS32 完成,编码器采用74LS148 和门电路完成

预置开关可用10 位拨码开关,计数脉冲采用实验箱上的开关和单脉冲发生器

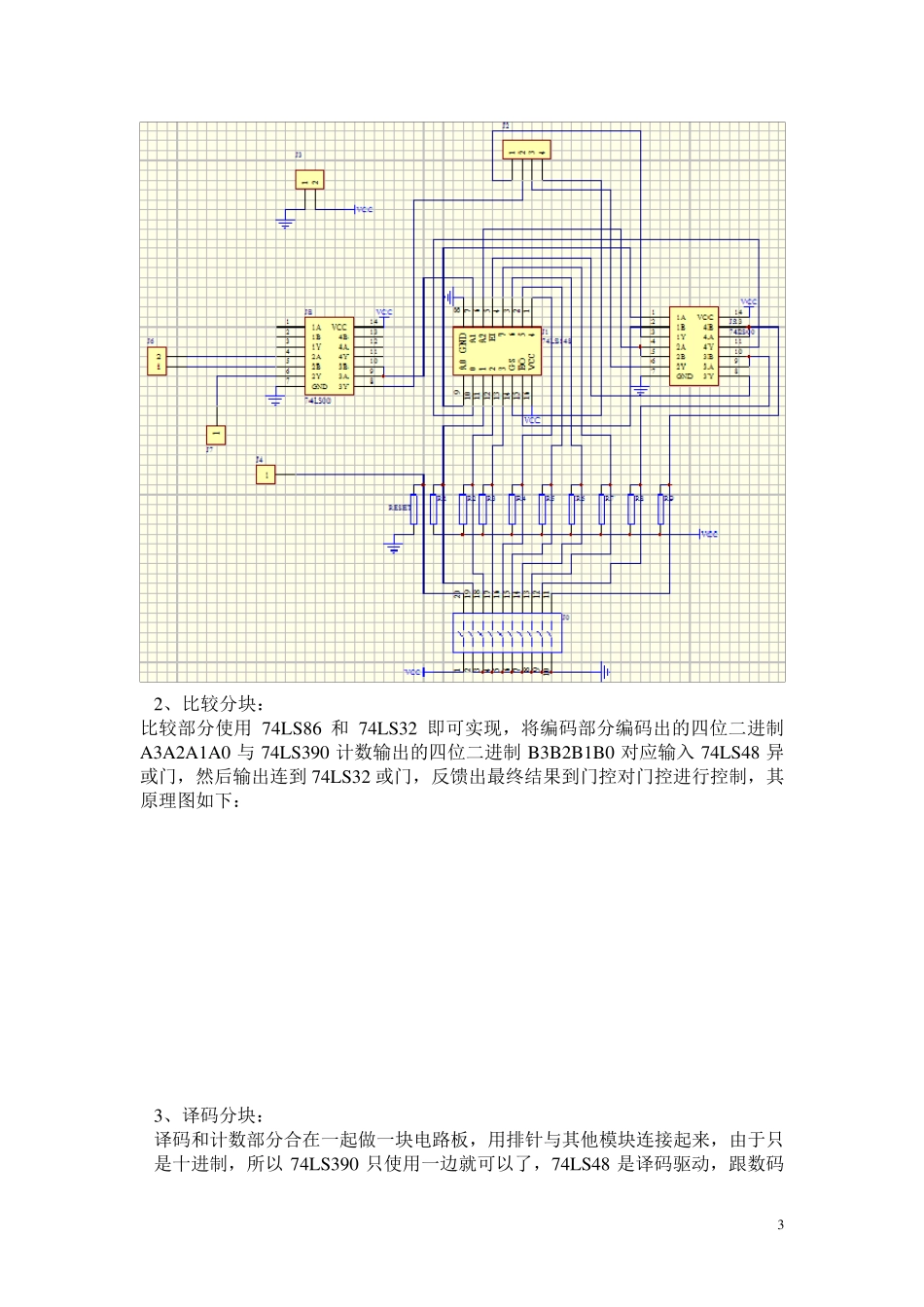

四、各单元电路设计 电路采用不同功能的模块分块来做,整个模块大体可分为三大分块:编码分块、译码分块、比较分块

然后用排线将各个子模块连接起来,各个部分的实现形式如下 : 1

、编码分块: 编码方案一:采用两 片 74LS148 数码管 译码驱动计数器 4 位数值比较器 编码器 预置开关 0-9 门 控 计数脉冲 控制信 号 图1 复位 2 因为一片74LS148 只实现对(0-7)的编码,而本电路要求要预置10 个数