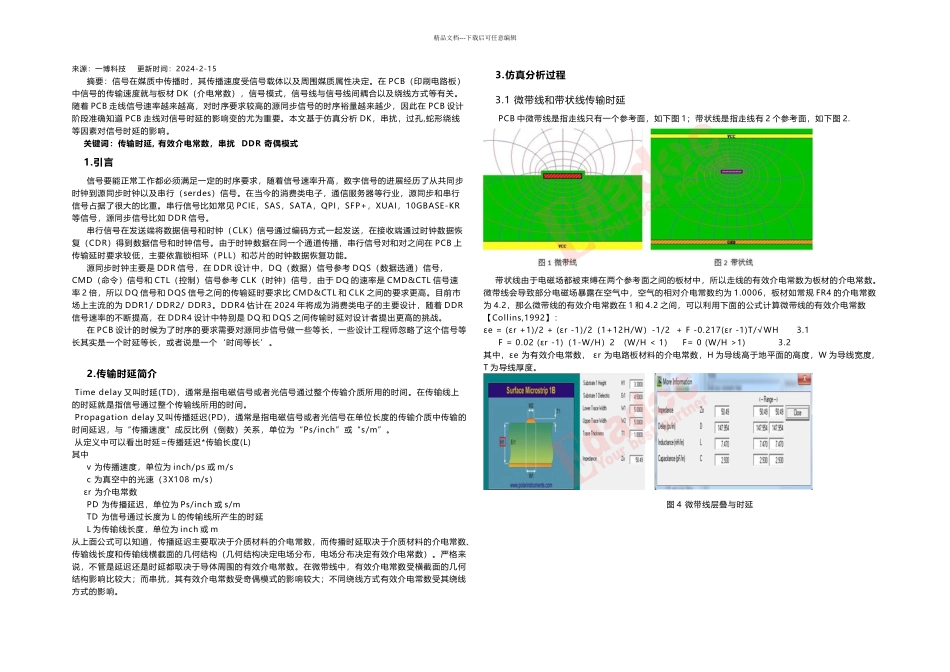

精品文档---下载后可任意编辑来源:一博科技 更新时间:2024-2-15 摘要:信号在媒质中传播时,其传播速度受信号载体以及周围媒质属性决定

在 PCB(印刷电路板)中信号的传输速度就与板材 DK(介电常数),信号模式,信号线与信号线间耦合以及绕线方式等有关

随着 PCB 走线信号速率越来越高,对时序要求较高的源同步信号的时序裕量越来越少,因此在 PCB 设计阶段准确知道 PCB 走线对信号时延的影响变的尤为重要

本文基于仿真分析 DK,串扰,过孔,蛇形绕线等因素对信号时延的影响

关键词:传输时延, 有效介电常数,串扰 DDR 奇偶模式 1

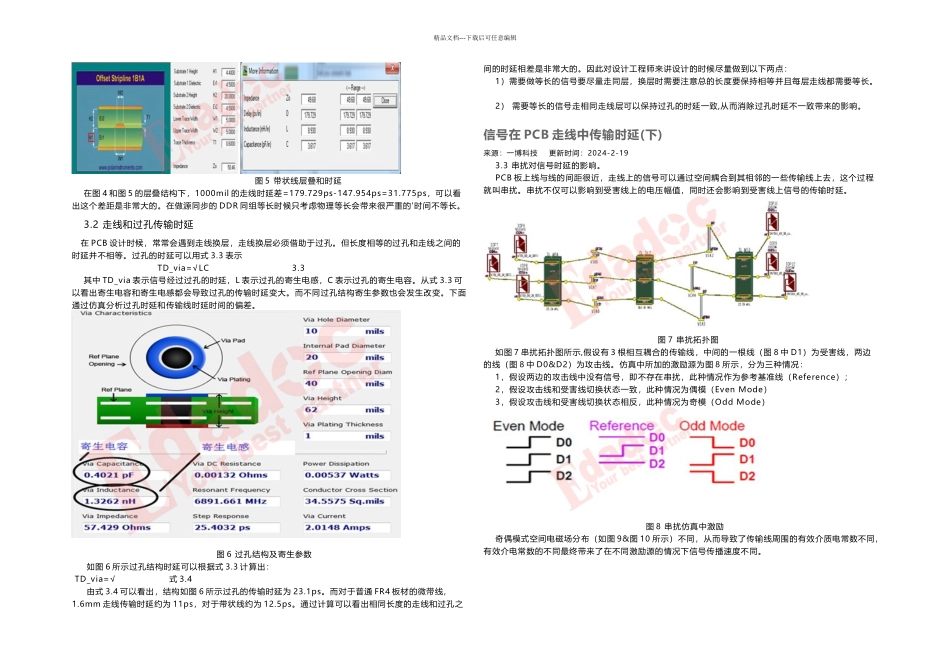

引言 信号要能正常工作都必须满足一定的时序要求,随着信号速率升高,数字信号的进展经历了从共同步时钟到源同步时钟以及串行(serdes)信号

在当今的消费类电子,通信服务器等行业,源同步和串行信号占据了很大的比重

串行信号比如常见 PCIE,SAS,SATA,QPI,SFP+,XUAI,10GBASE-KR等信号,源同步信号比如 DDR 信号

串行信号在发送端将数据信号和时钟(CLK)信号通过编码方式一起发送,在接收端通过时钟数据恢复(CDR)得到数据信号和时钟信号

由于时钟数据在同一个通道传播,串行信号对和对之间在 PCB 上传输延时要求较低,主要依靠锁相环(PLL)和芯片的时钟数据恢复功能

源同步时钟主要是 DDR 信号,在 DDR 设计中,DQ(数据)信号参考 DQS(数据选通)信号,CMD(命令)信号和 CTL(控制)信号参考 CLK(时钟)信号,由于 DQ 的速率是 CMD&CTL 信号速率 2 倍,所以 DQ 信号和 DQS 信号之间的传输延时要求比 CMD&CTL 和 CLK 之间的要求更高

目前市场上主流的为 DDR1/ DDR2/ DDR3

DDR4 估计在 2024 年将成为消费类电子的主要设计,随着 DDR信