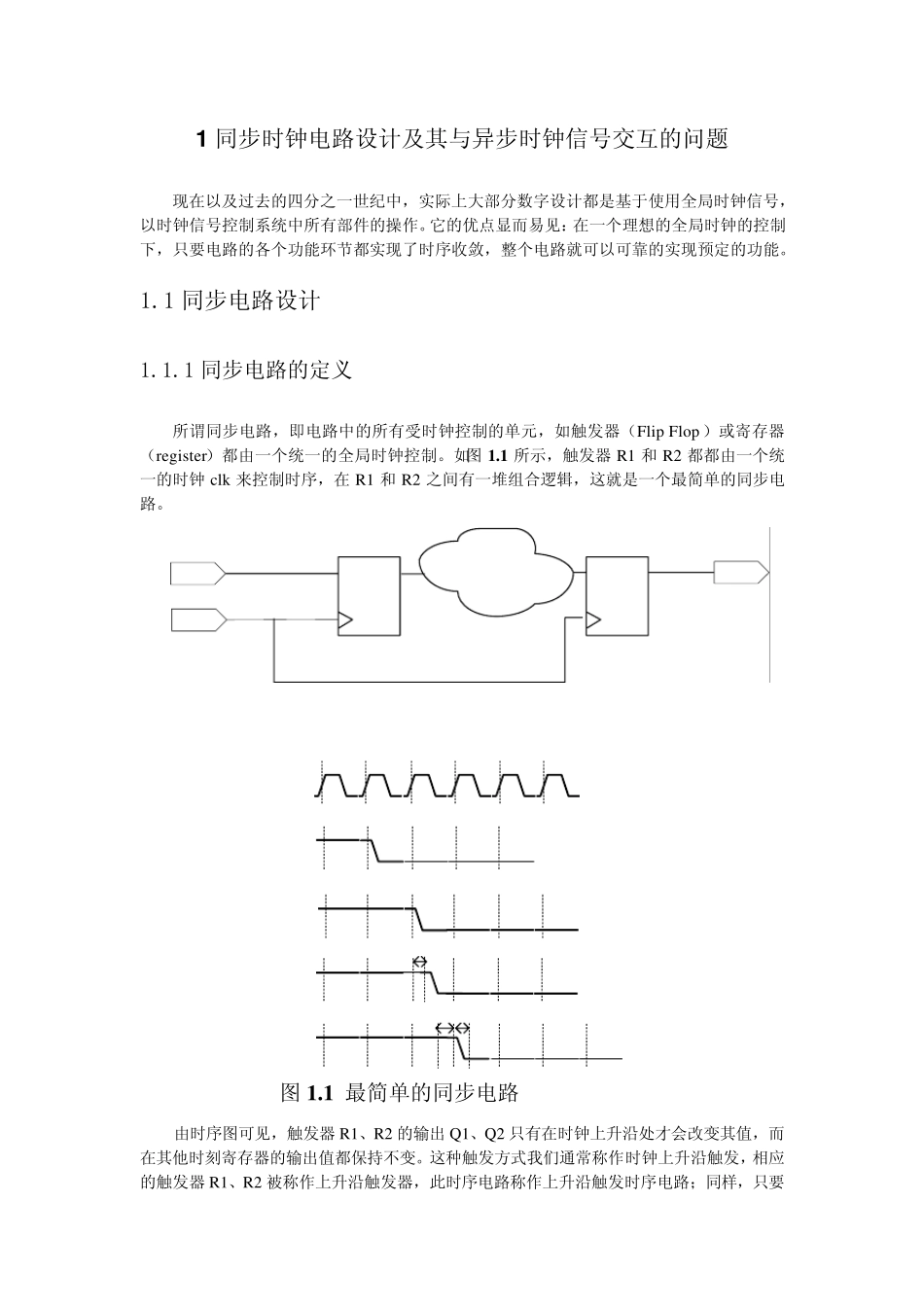

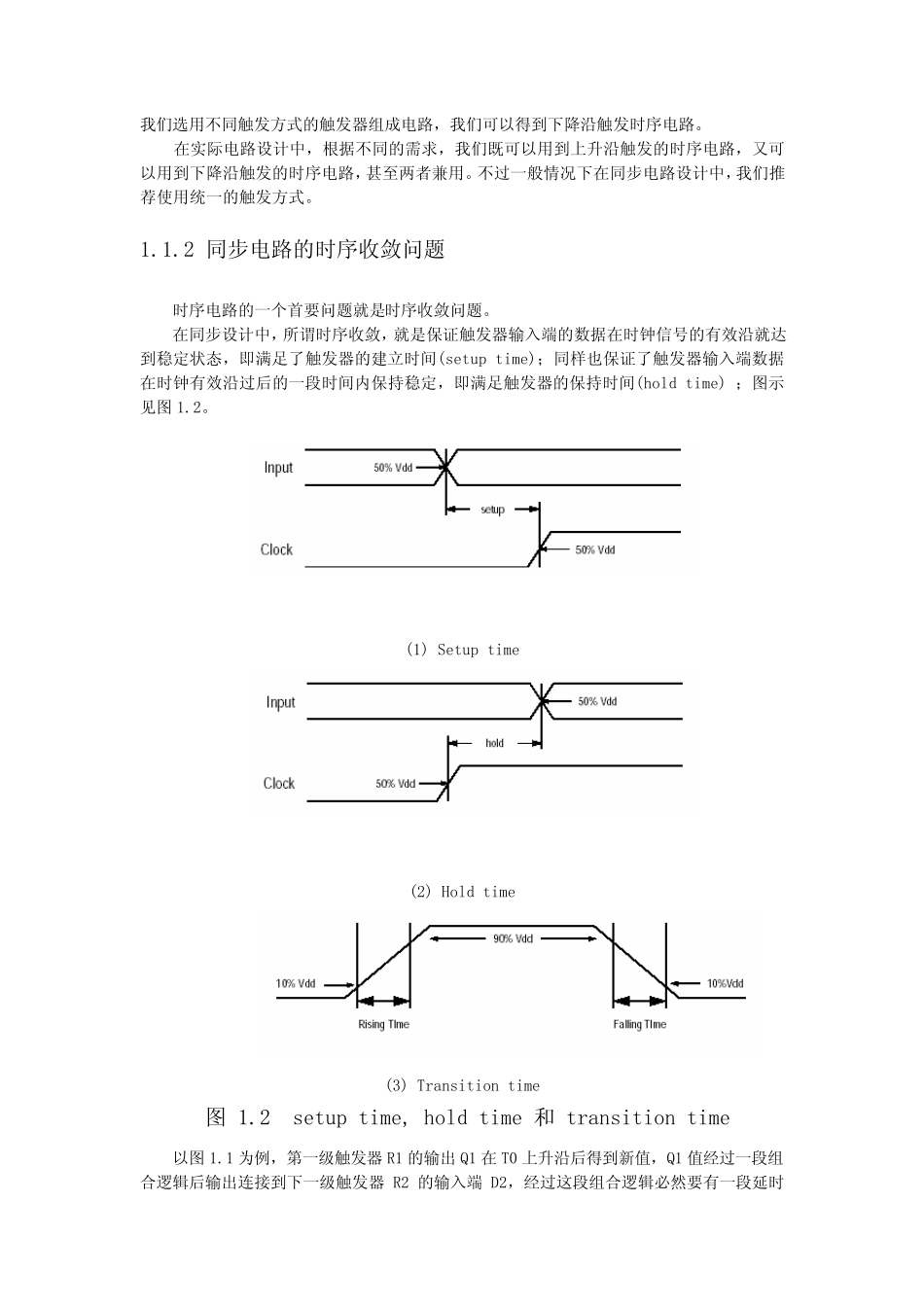

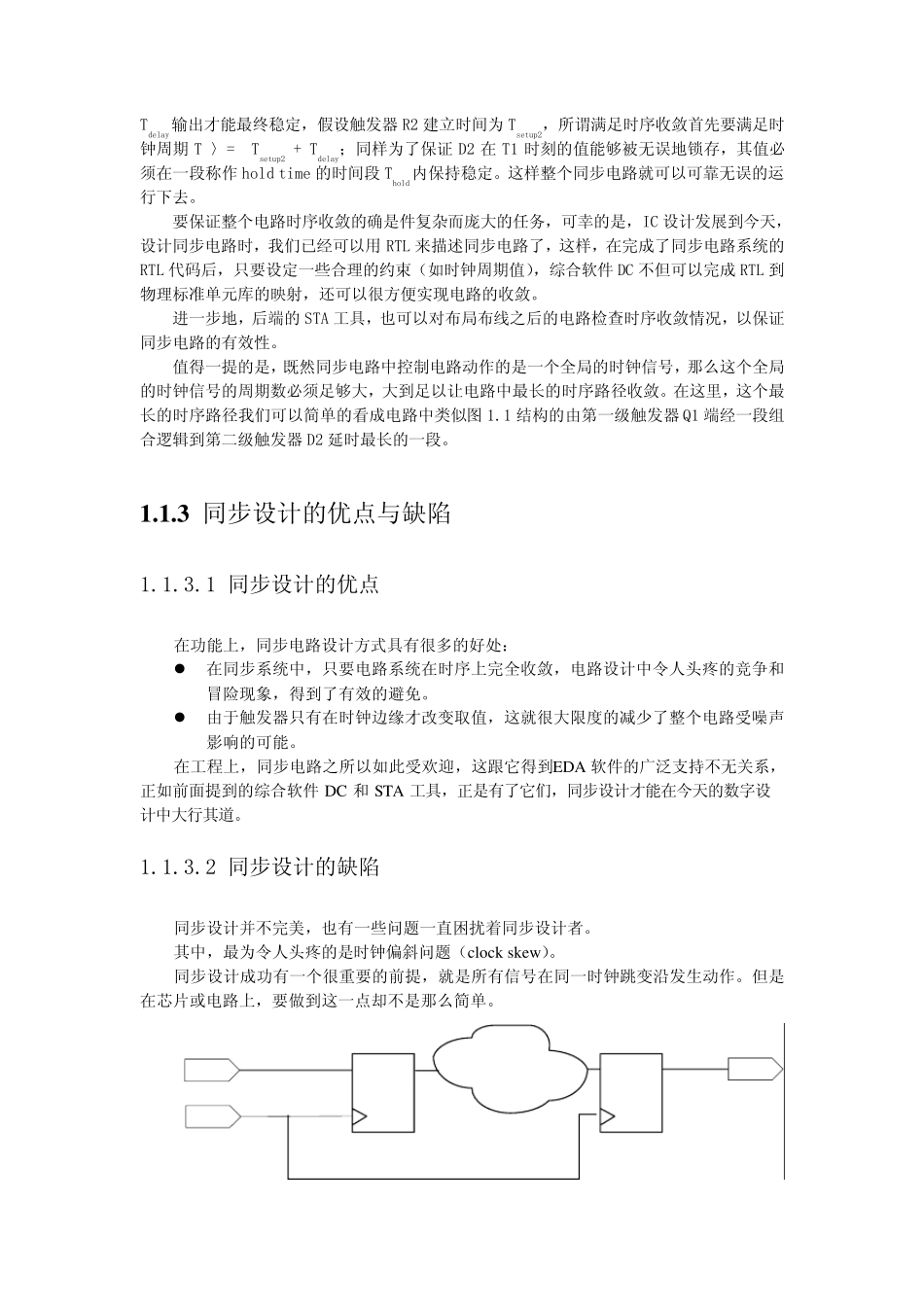

1 同步时钟电路设计及其与异步时钟信号交互的问题 现在以及过去的四分之一世纪中,实际上大部分数字设计都是基于使用全局时钟信号,以时钟信号控制系统中所有部件的操作。它的优点显而易见:在一个理想的全局时钟的控制下,只要电路的各个功能环节都实现了时序收敛,整个电路就可以可靠的实现预定的功能。 1.1 同步电路设计 1.1.1 同步电路的定义 所谓同步电路,即电路中的所有受时钟控制的单元,如触发器(Flip Flop )或寄存器(register)都由一个统一的全局时钟控制。如图1 .1 所示,触发器R1 和R2 都都由一个统一的时钟clk 来控制时序,在R1 和R2 之间有一堆组合逻辑,这就是一个最简单的同步电路。 图1 .1 最简单的同步电路 由时序图可见,触发器R1、R2 的输出 Q1、Q2 只有在时钟上升沿处才会改变其值,而在其他时刻寄存器的输出值都保持不变。这种触发方式我们通常称作时钟上升沿触发,相应的触发器R1、R2 被称作上升沿触发器,此时序电路称作上升沿触发时序电路;同样,只要我们选用不同触发方式的触发器组成电路,我们可以得到下降沿触发时序电路。 在实际电路设计中,根据不同的需求,我们既可以用到上升沿触发的时序电路,又可以用到下降沿触发的时序电路,甚至两者兼用。不过一般情况下在同步电路设计中,我们推荐使用统一的触发方式。 1.1.2 同步电路的时序收敛问题 时序电路的一个首要问题就是时序收敛问题。 在同步设计中,所谓时序收敛,就是保证触发器输入端的数据在时钟信号的有效沿就达到稳定状态,即满足了触发器的建立时间(setup time);同样也保证了触发器输入端数据在时钟有效沿过后的一段时间内保持稳定,即满足触发器的保持时间(hold time) ;图示见图 1.2。 (1) Setup time (2) Hold time (3) Transition time 图 1.2 setup time, hold time 和 transition time 以图 1.1 为例,第一级触发器R1 的输出 Q1 在 T0 上升沿后得到新值,Q1 值经过一段组合逻辑后输出连接到下一级触发器R2 的输入端 D2,经过这段组合逻辑必然要有一段延时Tdelay输出才能最终稳定,假设触发器R2 建立时间为Tsetup2,所谓满足时序收敛首先要满足时钟周期T 〉= Tsetup2 + Tdelay;同样为了保证D2 在T1 时刻的值能够被无误地锁存,其值必须在一段称作hold time 的时间段Thold内保持稳定。这样整个同步电路就可以可靠无误的运行下去。 要保证整个电路时序收敛的确是件复杂...