数字电子技术课程设计数字电子钟 指导老师:小组成员:目录摘要………………………………………………………………………………

3第一节 系统概述……………………………………………………………

4第二节单元电路设计与分析…………………………………………

6第三节 电路的总体设计与调试……………………………………

11第四节 设计总结……………………………………………………………

13附录部分芯片功能参数表…………………………………………

…14参考文献……………………………………………………………

……………17摘要数字钟是一个将“ 时”,“分”,“秒”显示于人的视觉器官的计时装置

它的计时周期为 24 小时,显示满刻度为 23 时 59 分 59 秒

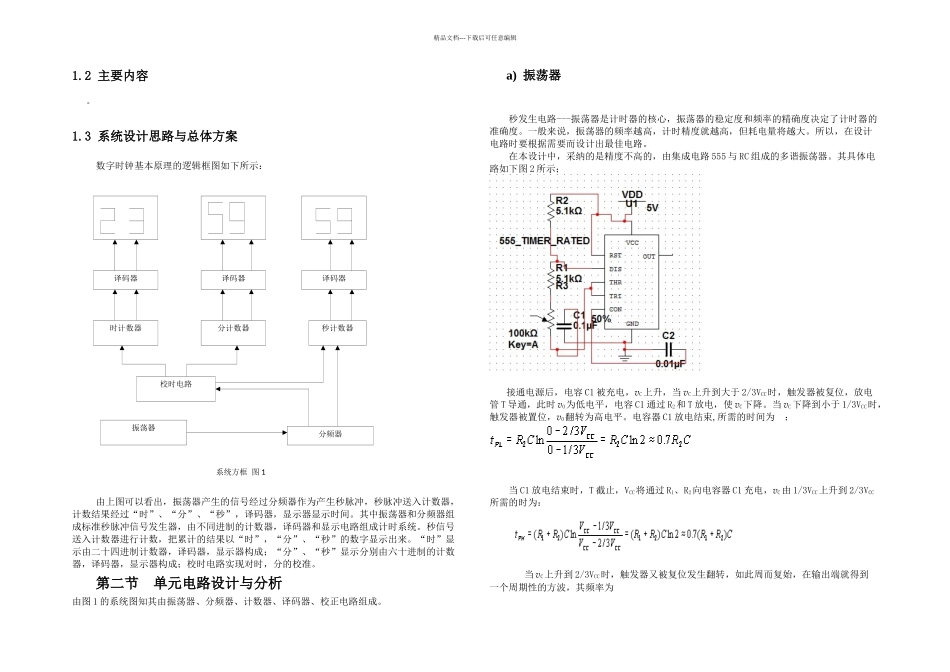

一个基本的数字钟电路主要由秒信号发生器、“时、分、秒、”计数器、译码器及显示器组成

由于采纳纯数字硬件设计制作,与传统的机械表相比,它具有走时准,显示直观,无机械传动装置等特点

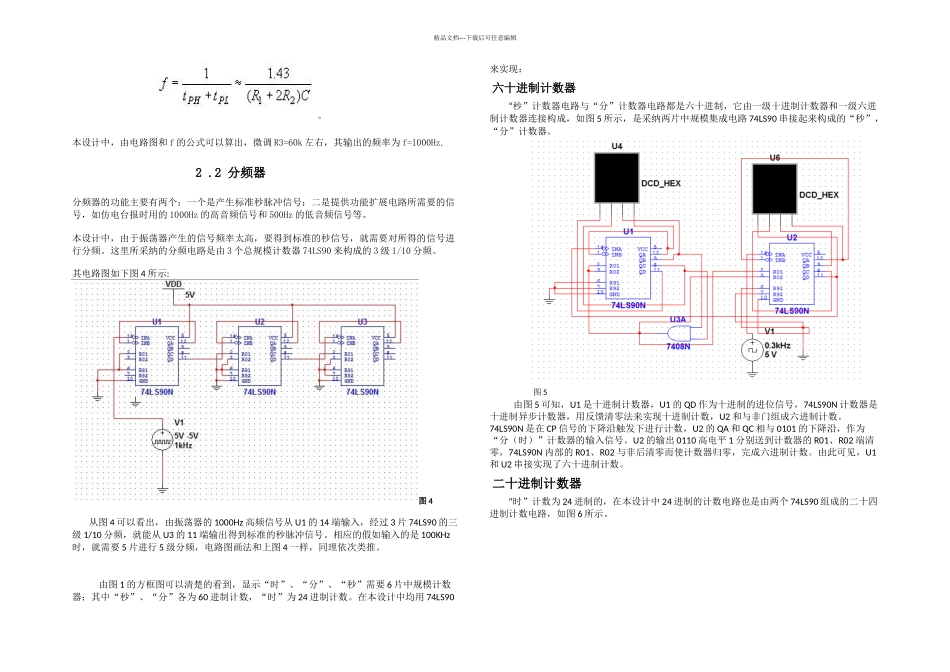

本设计中的数字时钟采纳数字电路实现对“时” 、“分”、“秒”的显示和调整

通过采纳各种集成数字芯片搭建电路来实现相应的功能

具体用到了 555 震荡器,74LS90 及与非,异或等门集成芯片等

该电路具有计时的功能

在对整个模块进行分析和画出总体电路图后,对各模块进行仿真并记录仿真所观察到的结果

实验证明该设计电路基本上能够符合设计要求

关键词振荡器、计数器、译码显示器、Multisim第一节 系统概述数字电子钟是由多块数字集成电路构成的,其中有振荡器,分频器,校时电路,计数器,译码器和显示器六部分组成

振荡器和分频器组成标准秒信号发生器,不同进制的计数器产生计数,译码器和显示器进行显示,通过校时电路实现对时,分的校准

掌握组合逻辑电路、时序逻辑电路及数字逻辑电路系统的设计、安装、测试方法;2)

进一步巩固所学的理论知识,提高运用所学知识分析