实验一 四位串行进位加法器的设计 一、实验目的 1

理解一位全加器的工作原理 2

掌握串行进位加法器的逻辑原理 3

进一步熟悉Quartus 软件的使用,了解设计的全过程, 二、实验内容 1

采用VHDL 语言设计四位串行进位的加法器 2

采用画原理图的方法设计四位串行进位加法器 三、实验步骤 1、使用VHDL 语言设计 1

打开File—>New Project Wizard 输入文件名 adder4 保存在 D 盘内,打开File—>New—>VHDL File,从模版中选择库的说明,use语句的说明,实体的说明,结构体的说明,编写 VHDL 代码,然后保存、编译

打开File—>New—>Other File—>Vector Waveform File,查找引脚,从 Edit 中选择 End Time 输入 40、ns 保存

从 Assignments—>Settings—>Simulator Settings—>Functional 然后 Processing—>Generate Functional Simnlation Netlist —>确定

选择 Start Simulation 保存最后的波形图,打开File—>close关闭工程

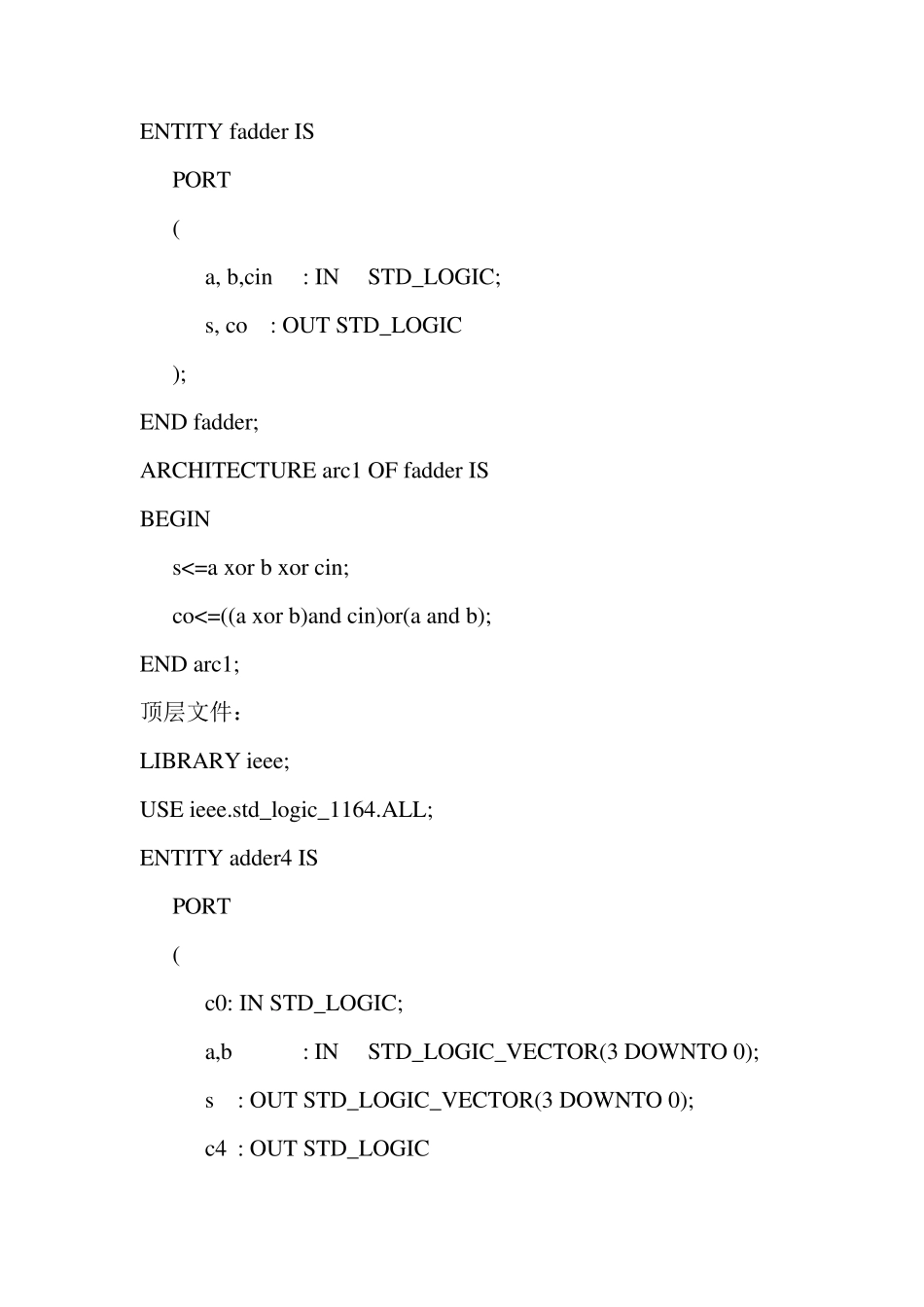

底层文件: LIBRARY ieee; USE ieee

std_logic_1164

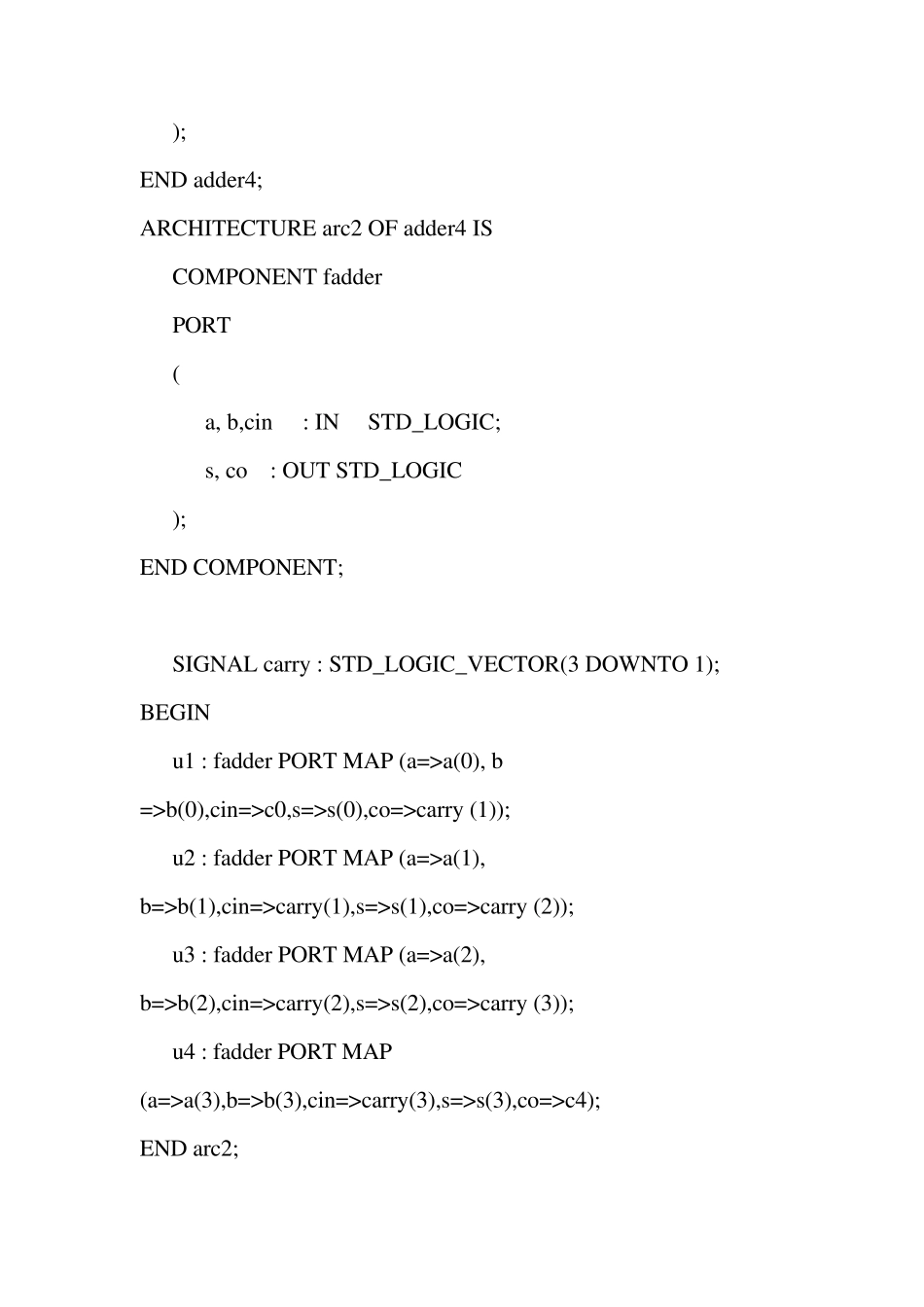

ALL; ENTITY fadder IS PORT ( a, b,cin : IN STD_LOGIC; s, co : OUT STD_LOGIC ); END fadder; ARCHITECTURE arc1 OF fadder IS BEGIN sb(0),cin=>c0,s=>s(0),co=>carry (1)); u2 : fadder PORT MAP (a=>a(1), b=>b(1),cin=>carry(1