实验三 用状态机实现序列检测器的设计 一、实验目的: 用状态机实现序列检测器的设计,并对其进行仿真和硬件测试

二、原理说明: 序列检测器可用于检测一组或多组由二进制码组成的脉冲序列信号,当序列检测器连续收到一组串行二进制码后,如果这组码与检测器中预先设置的码相同,则输出a,否则输出b

由于这种检测的关键在于正确码的收到必须是连续的,这就要求检测器必须记住前一次的正确码及正确序列,直到在连续的检测中所收到的每一位码都与预置数的对应码相同

在检测过程中,任何一位不相等都将回到初始状态重新开始检测

例3-1描述的电路完成对序列数"11100101"的

当这一串序列数高位在前(左移)串行进入检测器后,若此数与预置的密码数相同,则输出“a”,否则仍然输出“b”

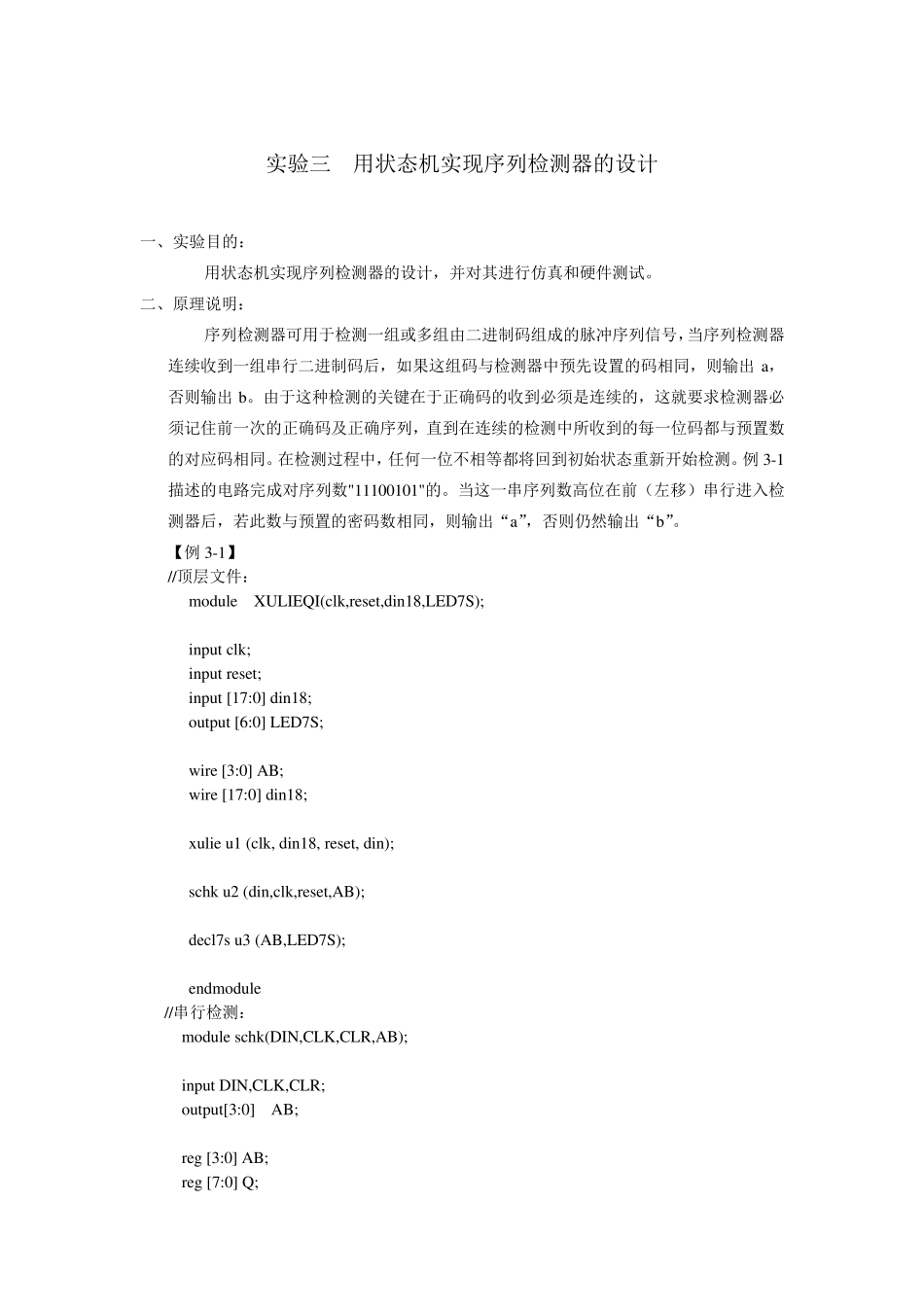

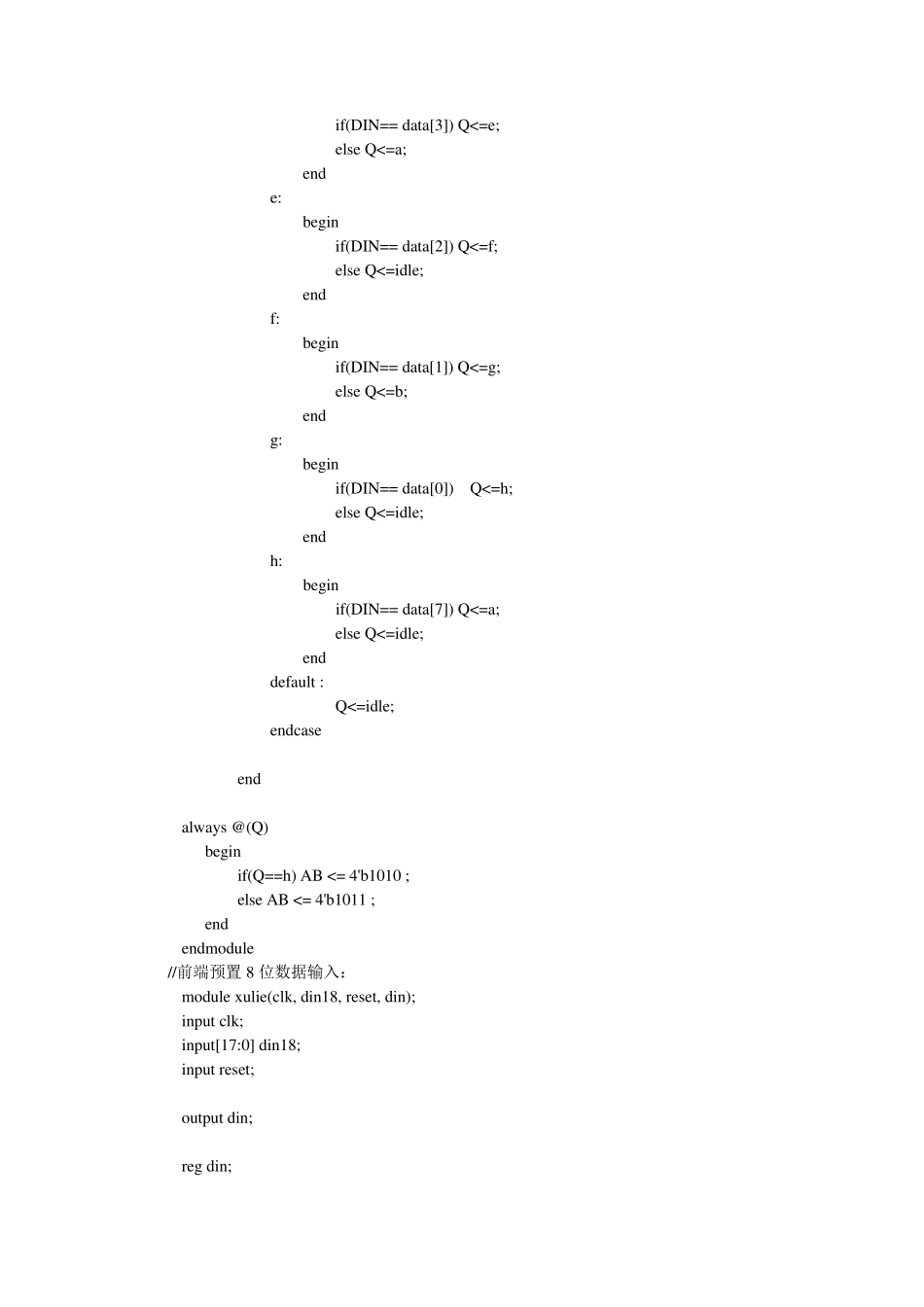

【例3-1】 //顶层文件: module XULIEQI(clk,reset,din18,LED7S); input clk; input reset; input [17:0] din18; output [6:0] LED7S; wire [3:0] AB; wire [17:0] din18; xulie u1 (clk, din18, reset, din); schk u2 (din,clk,reset,AB); decl7s u3 (AB,LED7S); endmodule //串行检测: module schk(DIN,CLK,CLR,AB); input DIN,CLK,CLR; output[3:0] AB; reg [3:0] AB; reg [7:0] Q; parameter idle = 8'b00000000, a = 8'b00000001, b = 8'b00000010, c = 8'b00000100, d = 8'b00001000,